Georgia Tech

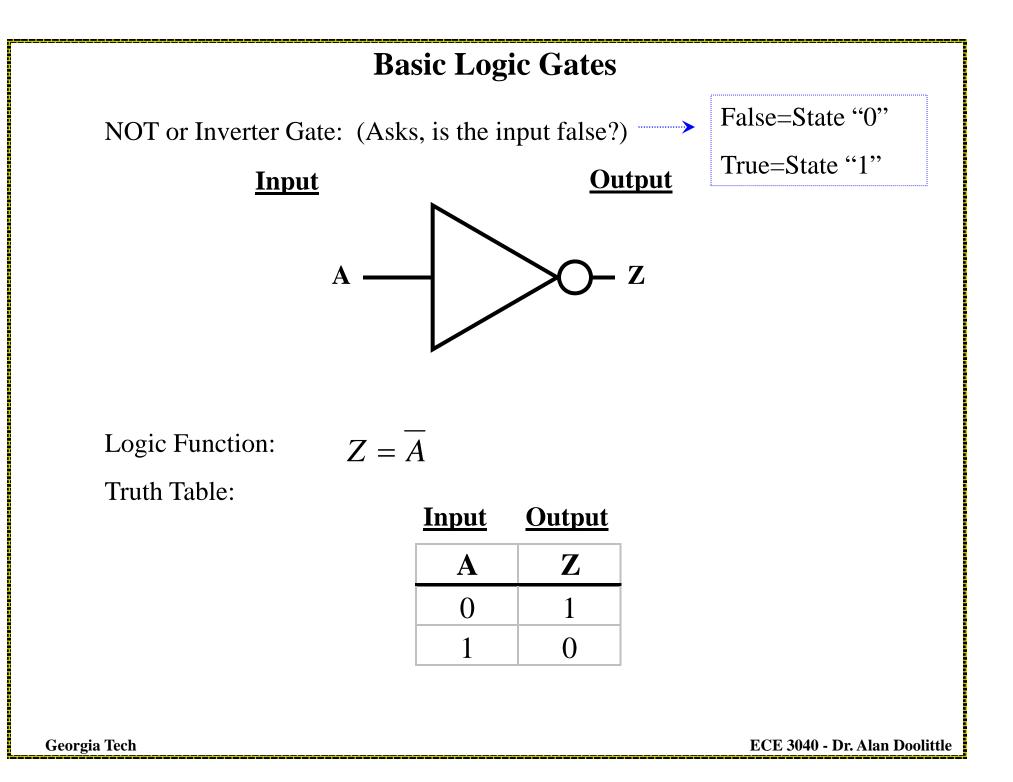

# **Basic Logic Gates**

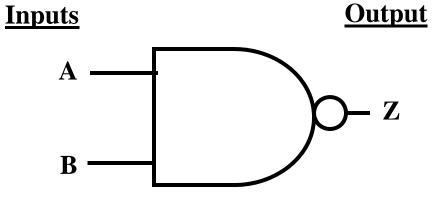

AND Gate: (Asks, are all inputs true?)

Logic Function:

$$Z = AB$$

Truth Table:

| <u>Inputs</u> |   | <u>Output</u> |

|---------------|---|---------------|

| Α             | B | Z             |

| 0             | 0 | 0             |

| 0             | 1 | 0             |

| 1             | 0 | 0             |

| 1             | 1 | 1             |

Georgia Tech

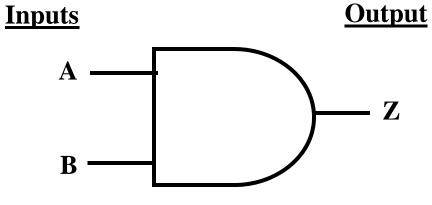

# **Basic Logic Gates**

OR Gate: (Asks, is any input true?)

Logic Function: Z = A + B

Truth Table:

| <u>Inputs</u> |   | <u>Output</u> |

|---------------|---|---------------|

| Α             | B | Z             |

| 0             | 0 | 0             |

| 0             | 1 | 1             |

| 1             | 0 | 1             |

| 1             | 1 | 1             |

Georgia Tech

# **Basic Logic Gates**

Any more complex functionality can be constructed from the three basic gates by using DeMorgan's Law:

$$\overline{ABC...N} = \overline{A} + \overline{B} + \overline{C}... + \overline{N}$$

The complement of the product is replaced with the sum of the complements

$$\overline{A+B+C+\ldots+N} = \overline{ABC}...\overline{N}$$

The complement of the sum is replaced with the product of the complements

Note: Only the AND, OR and Inverter gates are considered "Basic" logic Gates

Georgia Tech

NAND Gate: (Asks, is any input false?)

Logic Function:

$$Z = AB$$

Truth Table:

| <u>Inputs</u> |   | <u>Output</u> |  |

|---------------|---|---------------|--|

| Α             | B | Z             |  |

| 0             | 0 | 1             |  |

| 0             | 1 | 1             |  |

| 1             | 0 | 1             |  |

| 1             | 1 | 0             |  |

Georgia Tech

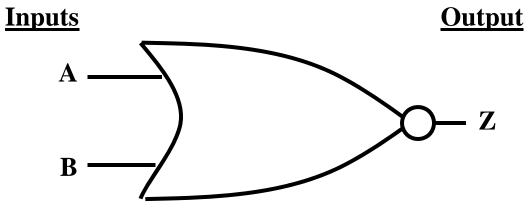

NOR Gate: (Asks, are all inputs false?)

Logic Function:

$$Z = A + B$$

Truth Table:

| <u>Inputs</u> |   | <u>Output</u> |  |

|---------------|---|---------------|--|

| Α             | B | Z             |  |

| 0             | 0 | 1             |  |

| 0             | 1 | 0             |  |

| 1             | 0 | 0             |  |

| 1             | 1 | 0             |  |

Georgia Tech

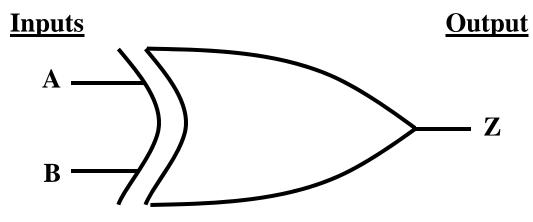

XOR Gate, Exclusive OR Gate: (Asks, are the inputs not equal? Inequality test)

Logic Function:

$$Z = AB + AB$$

Truth Table:

| <u>Inputs</u> |   | <u>Output</u> |  |

|---------------|---|---------------|--|

| Α             | B | Ζ             |  |

| 0             | 0 | 0             |  |

| 0             | 1 | 1             |  |

| 1             | 0 | 1             |  |

| 1             | 1 | 0             |  |

Georgia Tech

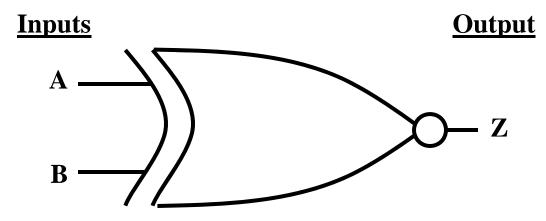

XNOR Gate, Exclusive NOR Gate: (Asks, are the inputs equal? An equality test)

Logic Function:

$$Z = \overline{\overline{AB} + A\overline{B}} = (\overline{A} + B)(A + \overline{B})$$

Truth Table:

| <u>Inputs</u> |   | <u>Output</u> |  |

|---------------|---|---------------|--|

| Α             | B | Ζ             |  |

| 0             | 0 | 1             |  |

| 0             | 1 | 0             |  |

| 1             | 0 | 0             |  |

| 1             | 1 | 1             |  |

Georgia Tech

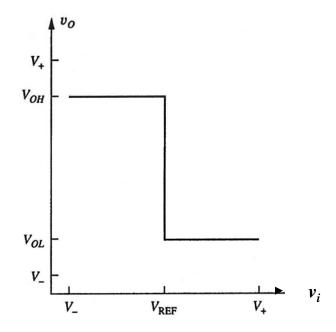

# **Ideal Inverter Characteristics**

•The easiest gate to analyze is the inverter (NOT) gate. By looking at the inverter we can learn a great deal about all gate physical implementations.

•The Voltage Transfer Characteristic (VTC) of an ideal inverter is:

Definitions:

- • $V_{OH}$ =Logic state "1" or "True". The highest possible output voltage.

- •V<sub>OL</sub>=Logic state "0" or "False". The Lowest possible output voltage.

- • $V_{REF}$ =Voltage for which the inverter switches from Logic state "1" to Logic state "0"

- •The transition is abrupt.

#### Georgia Tech

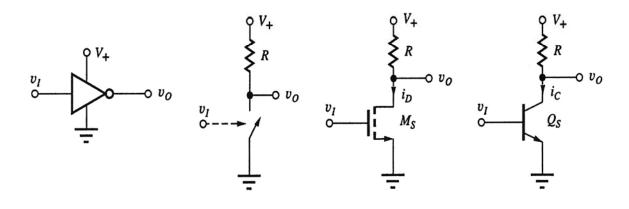

# **Actual Inverter Implementation**

•The simplest implementation of the inverter consists of a resistor and a switch.

•The switch can be an actual switch (user interaction required) or a transistor that is electrically "turned on or off".

| Closed Switch, Vo=V <sub>OL</sub> | Vo=0V | Vo=V <sub>DS</sub> of Ms | Vo=V <sub>CE</sub> of Qs |

|-----------------------------------|-------|--------------------------|--------------------------|

| <b>Open Switch, Vo=V</b> OH       | Vo=V+ | Vo=V+                    | Vo=V+                    |

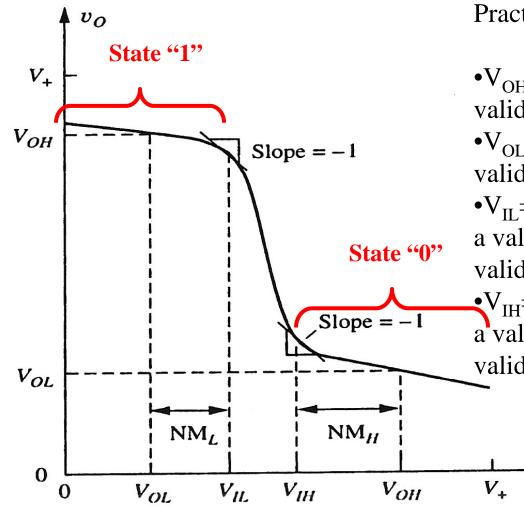

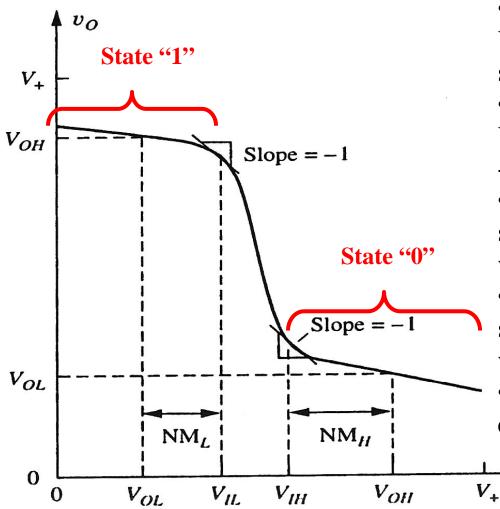

#### **Actual Inverter Characteristics**

Practical Definitions:

VI

• $V_{OH}$ = <u>Nominal</u> output voltage defining a valid logic state "1" at the output • $V_{OL}$ = <u>Nominal</u> output voltage defining a valid logic state "0" at the output • $V_{IL}$ =Maximum input voltage resulting in a valid logic state "0" at the input (or a valid logic state "1" at the output). • $V_{IH}$ = Minimum input voltage resulting in a valid logic state "1" at the input (or a valid logic state "1" at the input (or a valid logic state "1" at the input (or a

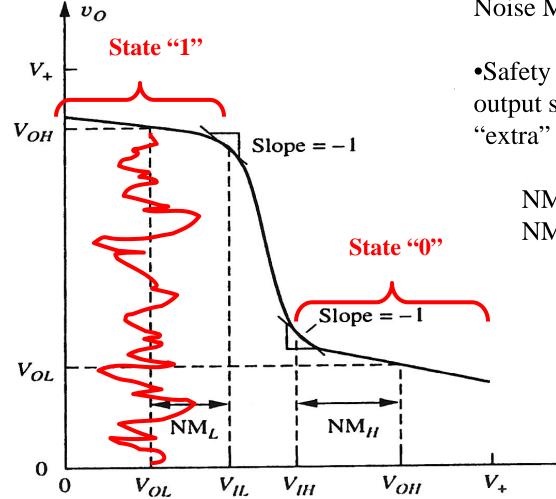

Georgia Tech

# **Actual Inverter Characteristics**

#### Noise Margins

•Safety Factor to insure that the output state does not change due to "extra" unwanted signals.

$\begin{array}{l} NM_{H} = V_{OH} - V_{IH} \\ NM_{L} = V_{IL} - V_{OL} \end{array}$

VI

Georgia Tech

#### **Actual Inverter Characteristics V**<sub>0</sub> V<sub>i</sub> $v_{O}$ $\mathbf{V}_{\!+}$ State "1" V<sub>OH</sub>- $V_+$ **NM<sub>H</sub>** $V_{OH}$ $\mathbf{V}_{\mathbf{IH}}$ -Slope = -1State "0" V<sub>IL</sub> NML Slope = -1VOL 0 V<sub>OL</sub>-NM<sub>L</sub> $NM_{H}$ 0 $v_I$ 0 V\_ – $V_{OH}$ $V_{+}$ $V_{IL}$ $V_{IH}$ $V_{OL}$ 0

Georgia Tech

## **Actual Inverter Characteristics**

Actual inverter transitions from  $V_{OH}$  to  $V_{OL}$  is not abrupt.

Definitions:

VI

- • $V_{IL}$ =Input voltage value (Larger than  $V_{OL}$ , defined in a moment) where the slope of the VTC equals -1

- • $V_{IH}$ =Input voltage value (Larger than  $V_{IL}$ ) where the slope of the VTC equals -1

- • $V_{OH}$ = The nominal output voltage for a state "1" at the output when the input voltage is  $V_{OL}$

- • $V_{OL}$ =The nominal output voltage for a state "0" at the output when the input voltage is  $V_{OH}$

- • $V_M$ =Voltage where the output voltage equals the input voltage

Georgia Tech

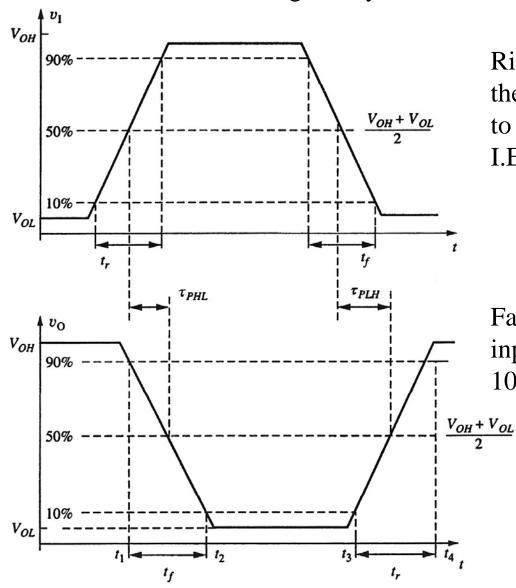

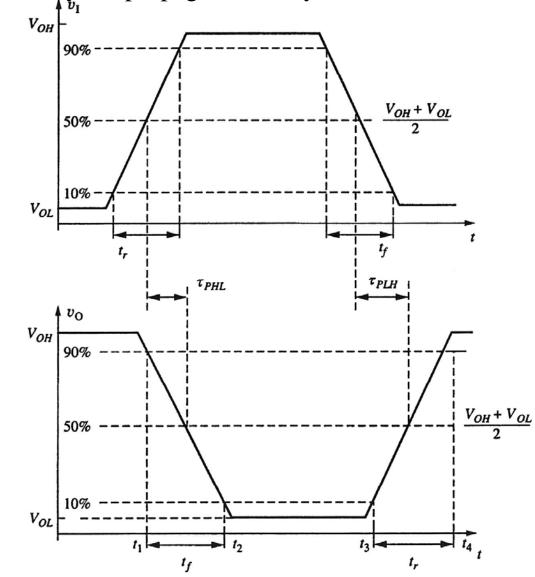

### **Inverter Time Response**

State transitions require finite amounts of time to occur. Thus, we can characterize the Rise, and Fall of the signals by:

Rise Time,  $t_r$ , = The time required for the input/output to transition from 10% to 90% of its total voltage excursion. I.E.:

$\Delta V = V_{OH} V_{OL}$  $V_{10\%} = V_{OL} + 0.1 \Delta V$  $V_{90\%} = V_{OL} + 0.9 \Delta V$

Fall Time,  $t_f$ , = The time required for the input/output to transition from 90% to 10% of its total voltage excursion.

### **Inverter Time Response**

State transitions require finite amounts of time to pass from the input of the gate to the output of the gate. This "time required for a state change" can be characterized by the propagation delays.

Propagation Delay from high-to-low,  $\tau_{PHL}$ , = The time delay between the 50% points on the input and output waveforms during the high-to-low output transition

Propagation Delay from low-to-high,  $\tau_{PLH}$ , = The time delay between the 50% points on the input and output waveforms during the low-to-high output transition

Average Propagation Delay,  $\tau_{P}=0.5(\tau_{PHL}+\tau_{PLH})$

The 50% points are:  $V_{50\%}=0.5(V_{OH}+V_{OL})$

# **Rise and Fall Time Dependence on Power**

Since larger currents can charge a capacitor faster, high speed requires higher power (for a fixed capacitor load).

Thus, there is a fundamental tradeoff in power and speed: Need high speed = Need higher power Need low power operation (example battery device) = will need to operate slower.