Georgia Tech

Georgia Tech

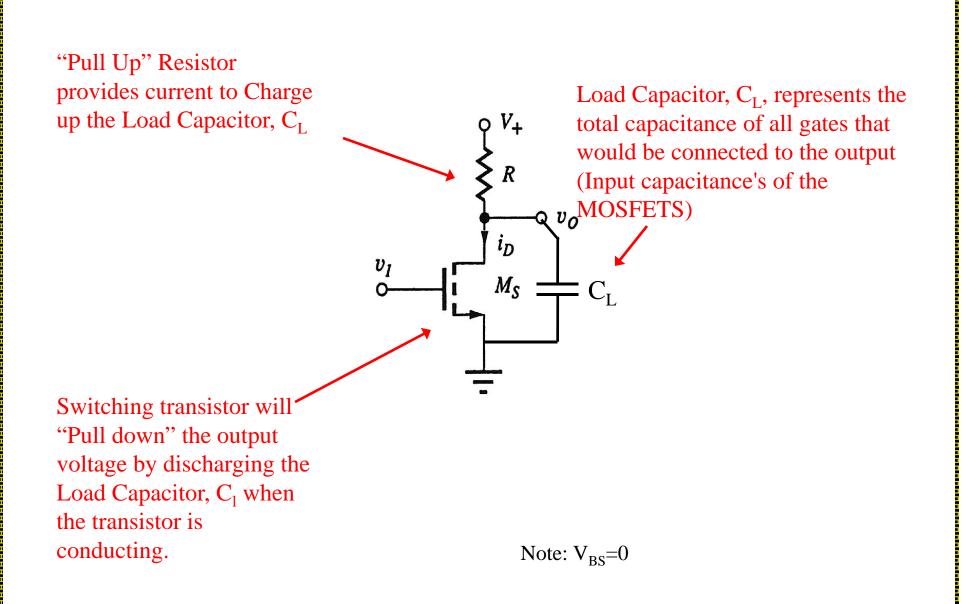

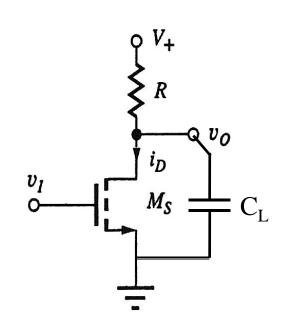

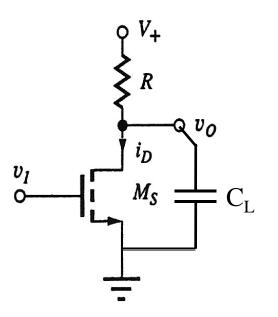

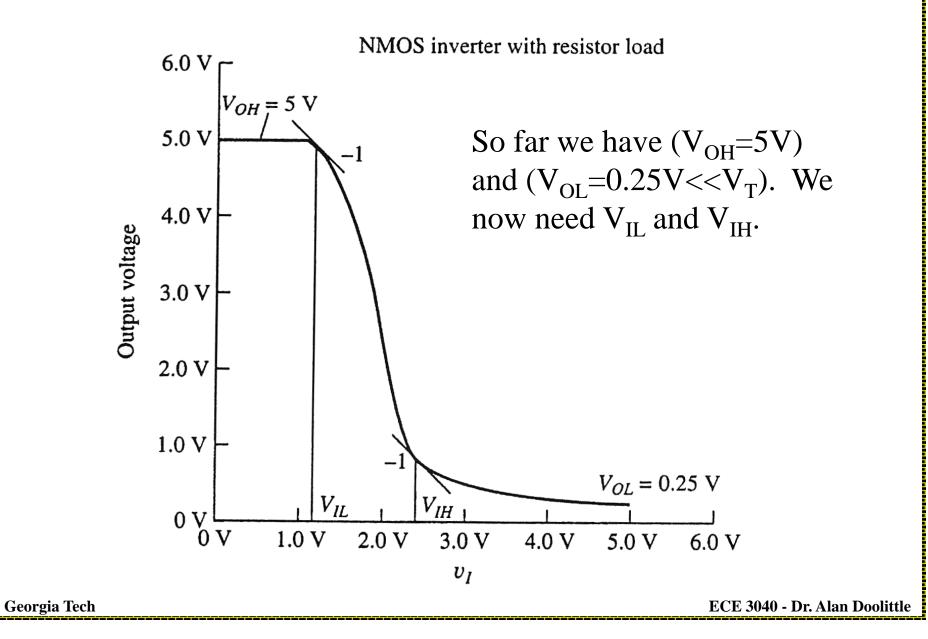

Inverter State: Input is Low Output is High

$$v_o = v_{DS} = V_{DD} - i_D R$$

For  $v_i = v_{GS} = V_{OL} < V_T$  $i_D = 0 \implies v_o = V_{DD} = V_{OH}$

$V_{OL} < V_T$  is our first design criteria!

For a nominal  $V_T = 1$ , we would typically make  $V_{OL} \sim 0.25V$  to insure adequate noise margin.

Georgia Tech

Inverter State: Input is High Output is Low

$$v_o = v_{DS} = V_{DD} - i_D R$$

For  $v_i = v_{GS} = V_{OH} = V_{DD}$  from previous page,  $v_o = V_{OL}$

Since  $v_{GS} = V_{DD} > v_{DS} \implies$  we must be in the linear region!

Georgia Tech

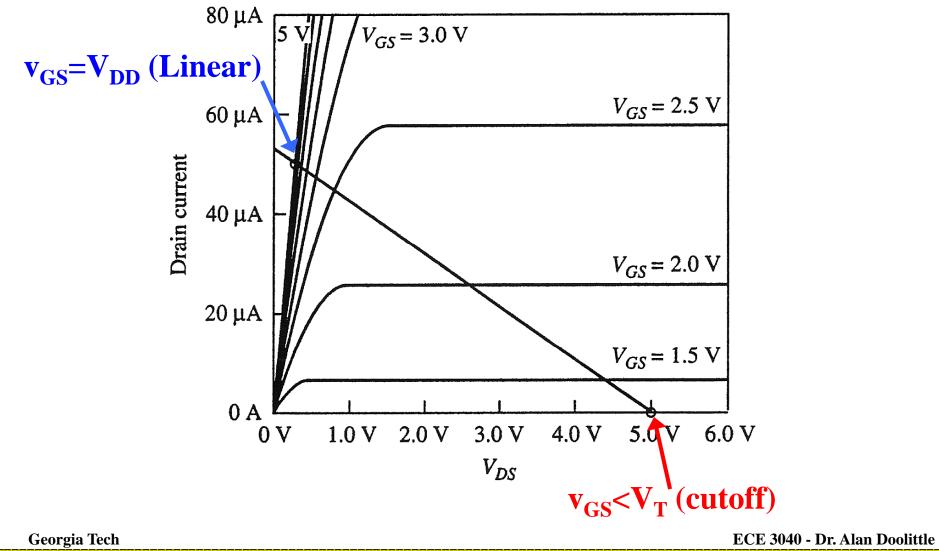

The MOSFET switches between the two operating points,  $v_{GS} < V_T$  (cutoff) and  $v_{GS} = V_{DD}$  (Linear) along a "Resistive" (linear IV characteristic) "Load Line" passing through the saturation region during the transition.

Example: If we wanted the gate to dissipate 0.25 mW using a  $V_{TN}=1V$  and  $K_n'=25e-6 \text{ A/V}^2$ , and having a  $V_{OL}=0.25V$ , what W/L ratio would be needed? What load resistance is required?

Since,  $Power = V_{DD} x i_{DS}$  $0.25e - 3 = 5i_{DS}$  $i_{DS} = 50 \mu A$  $i_{DS} = K'_{n} \left(\frac{W}{L}\right) (v_{GS} - V_{TN} - 0.5 v_{DS}) v_{DS}$  $50e - 6 = 25e - 6\left(\frac{W}{L}\right)(5 - 1 - .125)0.25$  $\left(\frac{W}{I}\right) = \frac{2.06}{1}$  $R = \frac{V_{DD} - V_{OL}}{i_{DD}} = \frac{5 - 0.25}{50e - 6} = 95 \ K\Omega$

Georgia Tech

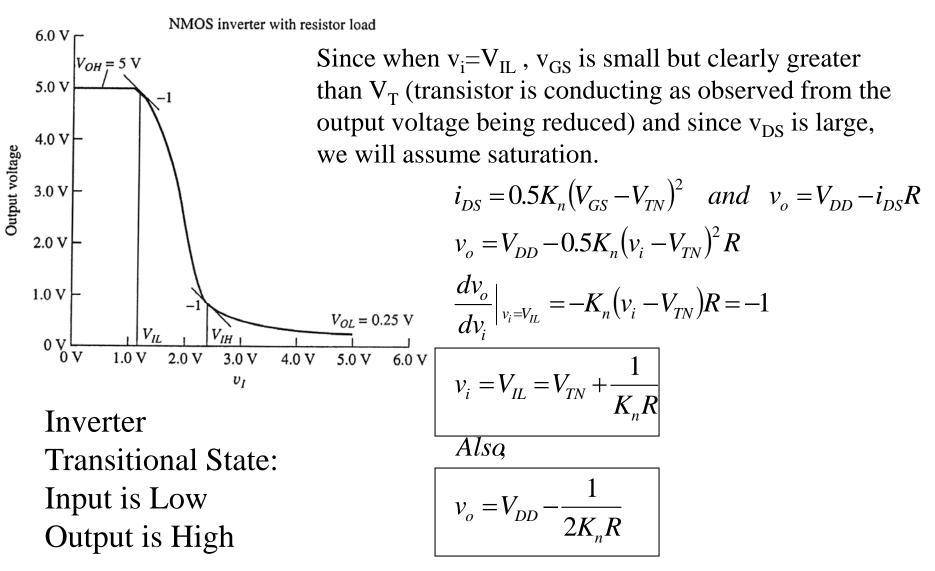

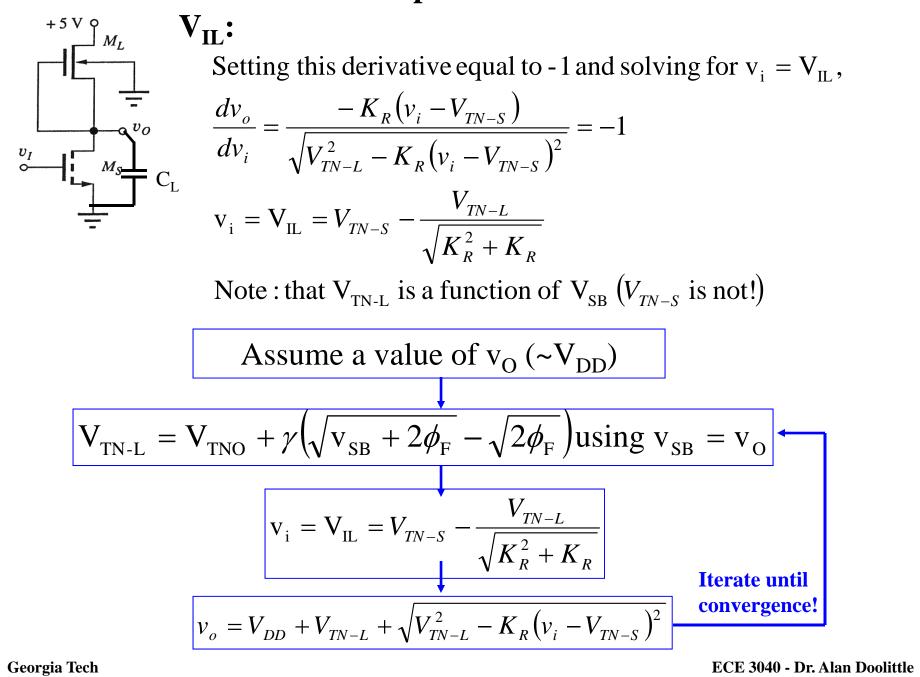

Calculating V<sub>IL</sub>

Georgia Tech

Example (cont'd): For our previous example,

$$v_i = V_{IL} = V_{TN} + \frac{1}{K_n R} = 1 + \frac{1}{25 \ e - 6 \left(\frac{2.06}{1}\right)95,000} = 1.2V$$

and,

$$v_o = V_{DD} - \frac{1}{2K_n R} = 5 - \frac{1}{2\left[25 \ e - 6\left(\frac{2.06}{1}\right)\right]} = 4.9V$$

Verifying our assumption of Saturation:  $v_{GS}-V_{TN} = 1.2-1 < v_{DS} = 4.9$

**Georgia Tech**

Calculating  $V_{IH}$

Since when  $v_i = V_{IH}$ ,  $v_{GS}$  is large and since  $v_{DS}$  is small, we will assume linear operation.

$$i_{DS} = K_n (v_{GS} - V_{TN} - 0.5v_{DS}) v_{DS} \quad and \quad v_o = V_{DD} - i_{DS} R$$

$$v_{GS} = v_i \quad and \quad v_{DS} = v_o$$

$$v_o = V_{DD} - K_n (v_i - V_{TN} - 0.5v_o) v_o R$$

$$\frac{v_o^2}{2} - v_o \left[ v_i - V_{TN} + \frac{1}{K_n R} \right] + \frac{V_{DD}}{K_n R} = 0$$

Setting  $\frac{dv_o}{dv_i} \Big|_{v_i = V_{IH}} = -1$  and solving for  $v_i$

$$v_i = V_{IH} = \left[ V_{TN} - \frac{1}{K_n R} + 1.63 \sqrt{\frac{V_{DD}}{K_n R}} \right]$$

Inverter

and,

Inverter

Transitional State:

Input is High

Output is Low

Georgia Tech

Calculating  $V_{IH}$

Example (cont'd): For our previous example,

$$V_{IH} = V_{TN} - \frac{1}{K_n R} + 1.63 \sqrt{\frac{V_{DD}}{K_n R}} = 2.44V$$

and,

$$v_o = \sqrt{\frac{2V_{DD}}{3K_n R}} = 0.83V$$

Thus, our Noise Margins are:

$$NM_{L} = V_{IL} - V_{OL} = 1.2 - 0.25 = 0.95V$$

and,

$$NM_{H} = V_{OH} - V_{IH} = 5 - 2.44 = 2.56V$$

This approach is good for single gate or small numbers of gates on a chip, but the large amount of area required to make the resistors prevent it from being used for very dense digital circuits. *We need a different approach!*

Georgia Tech

## **Procedure Summary**

- 1. <u>Select a  $V_{OL}$  based on a power specification or other design criteria such as noise margin, etc...</u> This is a fairly open parameter.

- 2. Determine what  $V_{OH}$  corresponds to this  $V_{OL}$ . When the switching transistor is off ( $v_i$ =this  $V_{OL}$ ), what  $V_{OH}$  results at the output?

- 3. Design the Switching Transistor for the required  $V_{OL}$ : Determine the L/W ratio needed to achieve this  $V_{OL}$  at the output for this  $V_{OH}$  at the input. To do this you have to properly identify what bias region you are in (linear, cutoff or saturation). Lower  $V_{OL}$  will require a wider transistor (more conductive) in order to "pull the output low". Lower VOH at the input will not "turn on the transistor as hard" and thus will also need a more conductive (wider) switching transistor.

- 4. Design the Load Resistor/Transistor for the required  $V_{OL}$ : Determine the required load (resistor or transistor L/W) needed to achieve this  $V_{OL}$  at the output for this  $V_{OH}$  at the input. If the load is a transistor (later) you will need to determine the proper bias mode linear, cutoff or saturation.

- 5. Find the Intermediate State 1/0 Edge voltages  $V_{IL}$  and  $V_{IH}$ : For  $V_{IL}$  and  $V_{IH}$  they are each found the same way. 1<sup>st</sup>, determine an appropriate voltage transfer function (relating  $v_i$  to  $v_o$ ) by setting the currents of the two devices equal. To do this, you will need to determine the proper bias mode linear, cutoff or saturation of each device. Next, take the derivative of the voltage transfer equation and set it equal to -1. Calculate the input voltage required for this slope to equal -1. This is by definition  $V_{IL}$  or  $V_{IH}$ . Note that  $V_{IL}$  and  $V_{IH}$  are two separate calculations and will have two different bias modes (i.e. different selections of linear, or saturation equations).

Georgia Tech

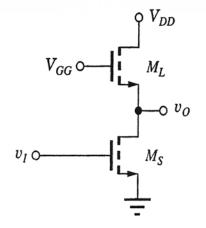

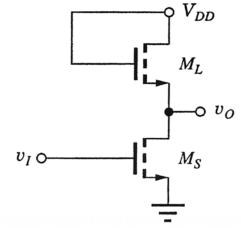

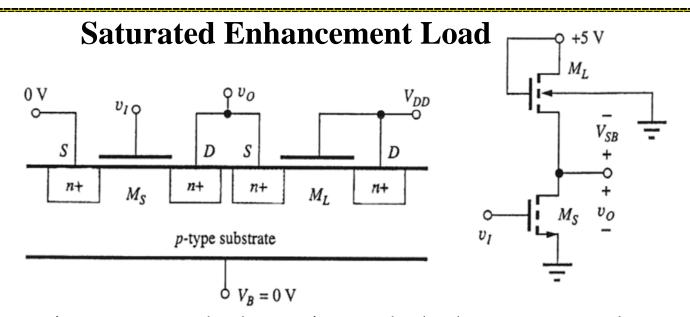

# **Our Options**

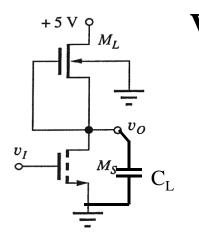

Depletion Load:

Linear Load:  $V_{GG} > V_{DD}$  so  $V_{GS-L} > V_{DS-L}$

Requires an extra power supply and is therefore, expensive! Saturated Enhancement Load:

$$V_{GS-L}-V_{TN} < V_{DS-L}$$

$-V_{TN} < 0$

Always Saturated (when on)

Georgia Tech

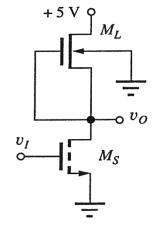

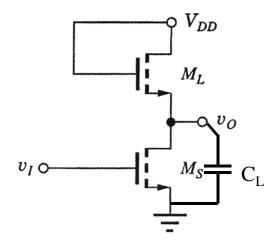

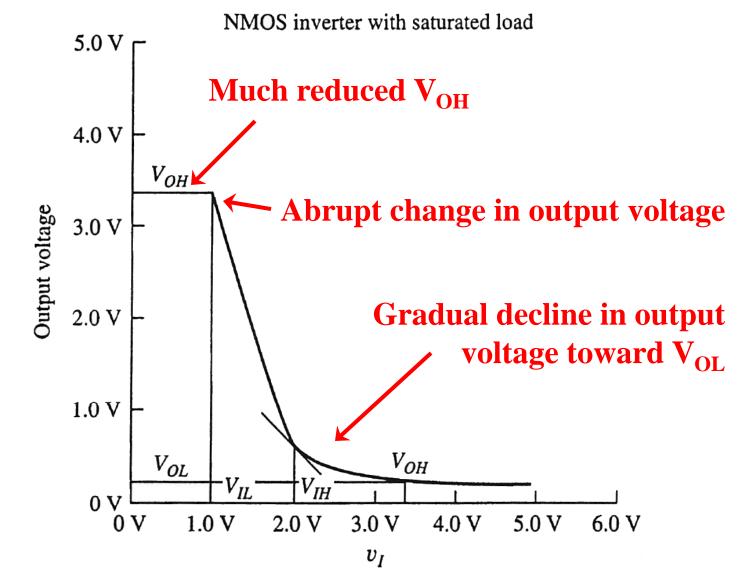

Inverter State: Input is Low Output is High

As before, for

$$v_i = v_{GS} = V_{OL} < V_T$$

$i_{DS-S} = 0$

$V_{OL} < V_T$  is our first design criteria!

For a nominal  $V_T = 1$ , we would typically make  $V_{OL} \sim 0.25V$  to insure adequate noise margin.

**Georgia Tech**

V<sub>GS-L</sub>=V<sub>DS-L</sub>

For  $v_i = v_{GS} = V_{OH}$ ,  $M_S$  and  $M_L$  conduct their maximum amount of current.

$$v_0 = V_{0L} = 0.25V$$

so,

$$V_{\text{DS-L}} = V_{\text{DD}} - v_{\text{O}} = 4.75 \text{V}$$

$$i_{DS-L} = \frac{K_n}{2} \left( \frac{W}{L} \right) \Big|_L (v_{GS-L} - V_{TN})^2$$

Using the same power design spec (0.25mW) and device parameters as before,

$$i_{DS-L} = 50uA$$

, so

Inverter State: Input is High Output is Low

$$50e - 6 = 12.5e - 6\left(\frac{W}{L}\right)\Big|_{L} (4.75 - 1)^{2}$$

$$\left(\frac{W}{L}\right)\Big|_{L} = 0.284$$

Georgia Tech

$$\left(\frac{W}{L}\right)\Big|_{L} = 0.284$$

Since we normally reference the width to length ratio in terms of it's "smallest dimension that we can fabricate" (as of 2001 this is ~0.07 um in the lab, 0.18 um in production) we can express this in an alternative form. For our discussion, we will assume (for mathematical simplicity) that this smallest feature size is 1um. Thus,

$$\left(\frac{W}{L}\right)_{L} = \frac{1}{3.52}$$

ECE 3040 - Dr. Alan Doolittle

Georgia Tech

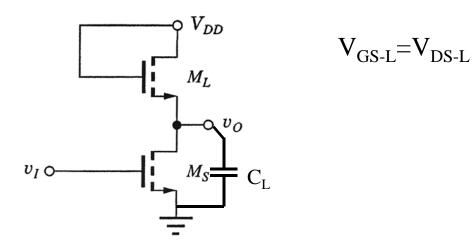

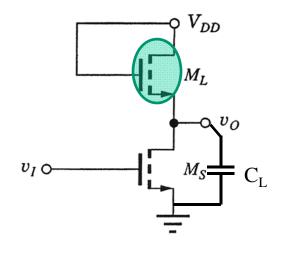

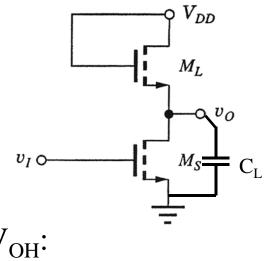

**Inverter State:** Input is Low Output is High

V<sub>OH</sub>:

When  $M_s$  is off,  $C_L$  charges up through  $M_I$ , reducing  $V_{DS-L}$  until

$$V_{TN} = V_{GS-L} = V_{DS-L}$$

At this point, M<sub>I</sub> cuts off preventing further charging.

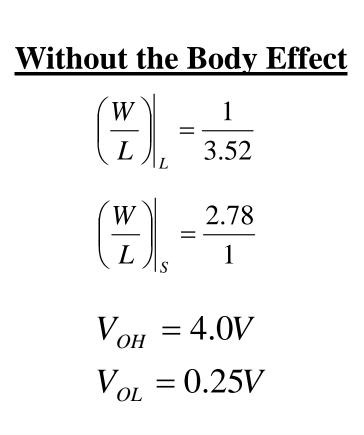

Thus, when  $v_0 = V_{OH}$ ,  $v_{GS-L} = V_{DD} - V_{TN}$  or  $V_{OH} = V_{DD} - V_{TN} = 5 - 1 = 4V$

V<sub>OH</sub> is significantly reduced from it's previous (with resistive load) value!

**Georgia Tech**

Georgia Tech

Combining the results from before we see that our Load Transistor is much longer than it is wide, while our switching transistor is wider than it is long.

$$\left(\frac{W}{L}\right)\Big|_{L} = \frac{1}{3.52} \qquad \qquad \left(\frac{W}{L}\right)\Big|_{S} = \frac{2.78}{1}$$

ECE 3040 - Dr. Alan Doolittle

Georgia Tech

Since the substrate is common to both transistors, the body-to-source voltage,  $v_{SB}$ , varies as the output voltage varies. Thus, the threshold voltage varies resulting in a variation in  $V_{OH}$

$$\begin{split} V_{OH} &= V_{DD} - V_{TN-L} \\ V_{OH} &= V_{DD} - \left[ V_{TO} + \gamma \left( \sqrt{v_{SB} + 2\phi_F} - \sqrt{2\phi_F} \right) \right] \\ V_{OH} &= V_{DD} - \left[ V_{TO} + \gamma \left( \sqrt{V_{OH} + 2\phi_F} - \sqrt{2\phi_F} \right) \right] \end{split}$$

In writing the above equation we have only examined the condition when  $v_{SB}-V_{OH}$ . Since  $v_{SB}-v_{O}$ , the threshold voltage is continuously varying as the device is switched, introducing an additional level of "non-linearity"  $(v_{O}=f(v_{O}) \text{ and } i_{DS}=f(v_{O}) )$ . Georgia Tech ECE 3040 - Dr. Alan Doolittle

$$If \ \gamma = 0.5 \ \sqrt{V} \quad and \quad 2\phi_F = 0.6V$$

$$V_{OH} = V_{DD} - \left[V_{TO} + \gamma \left(\sqrt{V_{OH} + 2\phi_F} - \sqrt{2\phi_F}\right)\right]$$

$$V_{OH} = 5 - \left[1 + 0.5 \left(\sqrt{V_{OH} + 0.6} - \sqrt{0.6}\right)\right]$$

or

$$V_{OH}^{2} - 9.03V_{OH} + 19.1 = 0$$

$V_{OH} = 3.39V \text{ or } 5.54V$

Georgia Tech

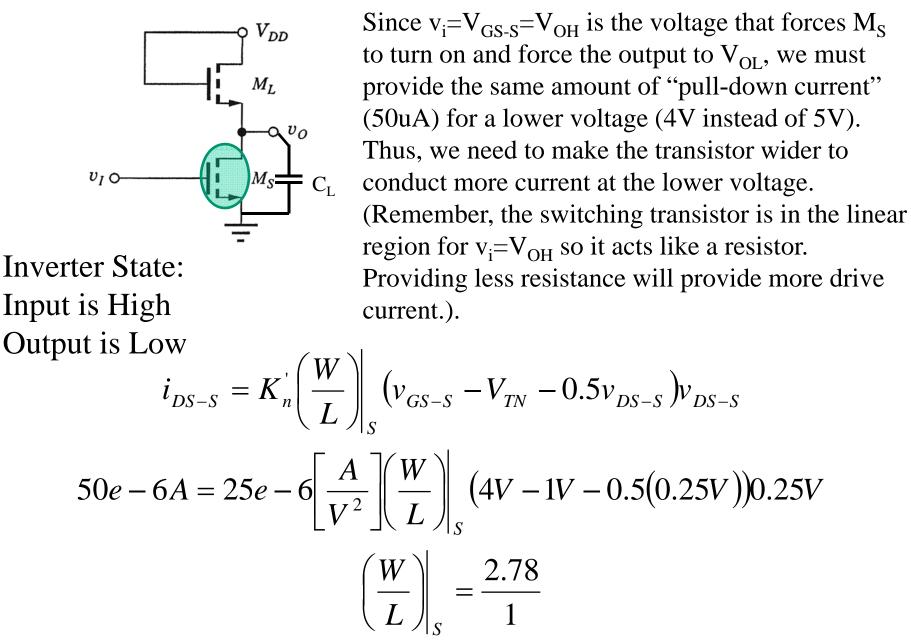

Since the body effect changes  $V_{TN}$ , we need to readjust the width to length ratios of both transistors:

$M_S$ :  $V_{OH}$  is lower than what we used before, so we need the same current at a lower voltage--make the switching transistor even wider!

$$i_{DS-S} = K'_{n} \left(\frac{W}{L}\right) \Big|_{S} (v_{GS-S} - V_{TN} - 0.5v_{DS-S}) v_{DS-S}$$

$$50e - 6A = \dots$$

$$\dots 25e - 6\left[\frac{A}{V^2}\right]\left(\frac{W}{L}\right)\Big|_{S} (3.39V - 1V - 0.5(0.25V))0.25V$$

$$\left(\frac{W}{L}\right)\Big|_{S} = \frac{3.59}{U}$$

Inverter State:

Input is High Output is Low

ECE 3040 - Dr. Alan Doolittle

**Georgia Tech**

$\left| L \right|_{S}$

Inverter State: Input is High Output is Low

$$\begin{split} V_{TN-L} &= V_{TO} + \gamma \left( \sqrt{v_{SB} + 2\phi_F} - \sqrt{2\phi_F} \right) \\ V_{TN-L} &= 1 + 0.5 \left( \sqrt{0.25 + 0.6} - \sqrt{0.6} \right) \\ V_{TN-L} &= 1.07V \end{split}$$

$M_{L}$ : When  $v_i = V_{OH}$ ,  $v_o = V_{OL} = v_{SB} = 0.25V$

$$i_{DS-L} = \frac{K'_n}{2} \left(\frac{W}{L}\right) \Big|_L (v_{GS-L} - V_{TN-L})^2$$

50e - 6 = 12.5e - 6  $\left(\frac{W}{L}\right) \Big|_L (4.75 - 1.07)^2$

$\left(\frac{W}{L}\right) \Big|_L = \frac{1}{3.39}$

ECE 3040 - Dr. Alan Doolittle

Georgia Tech

So the body effect requires that:

# With the Body Effect

| $\left( \underline{W} \right)$ | - | <br>1    |

|--------------------------------|---|----------|

| $\left( L \right)$             | L | <br>3.39 |

| $\left( \begin{array}{c} W \end{array} \right)$ |   |   | 3.53 |

|-------------------------------------------------|---|---|------|

| $\left( \frac{1}{L} \right)$                    | S | _ | 1    |

$$V_{OH} = 3.4V$$

$$V_{OL} = 0.25V$$

**Georgia Tech**

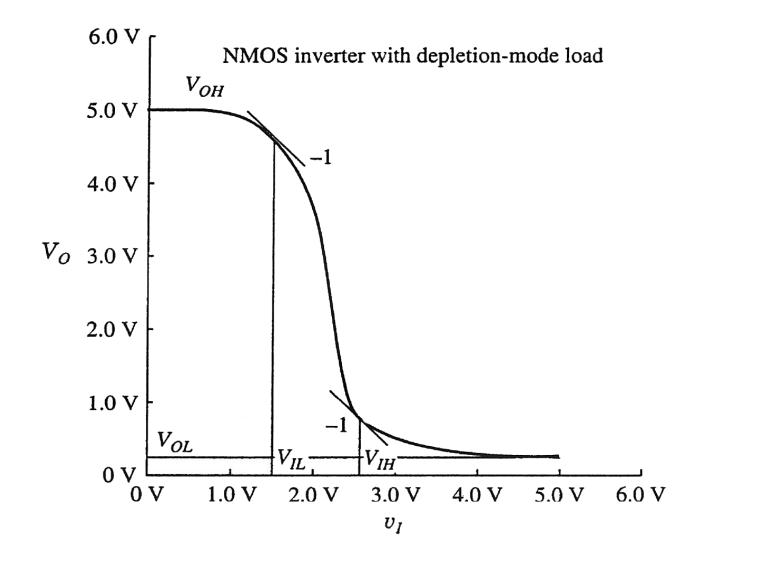

#### Saturated load VTC

Georgia Tech

The abrupt nature of this transition is due to  $V_{TN-S} < V_{TN-L}$  due to the body effect. Thus, as  $M_S$  begins to conduct,  $M_L$  is off.

Georgia Tech

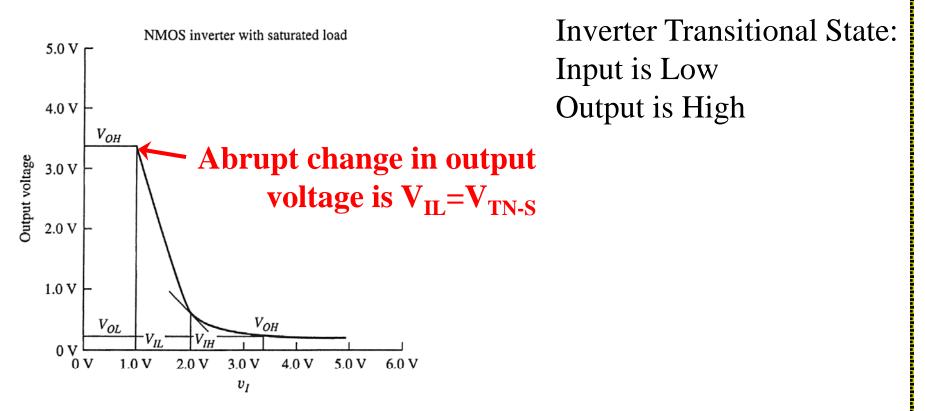

Find V<sub>IH</sub>:

Inverter Transitional State: Input is High Output is Low

$$\begin{split} i_{DS-S} &= i_{DS-L} \\ K_{n-S} \left( v_{GS-S} - V_{TNS} - 0.5 v_{DS-S} \right) v_{DS-S} = K_{n-L} \left( v_{GS-L} - V_{TNL} \right)^2 \\ K_{n-S} \left( v_i - V_{TNS} - 0.5 v_o \right) v_o &= K_{n-L} \left( V_{DD} - v_o - V_{TNL} \right)^2 \\ solving for v_i, \\ v_i &= V_{TNS} + 0.5 v_o + \frac{K_{n-L}}{2K_{n-S}} \left[ \frac{V_{DD} - V_{TNL}}{v_o} - 2 \left( V_{DD} - V_{TNL} \right) + v_o \right] \\ Assume \frac{dv_o}{dv_i} &= \left( \frac{dv_i}{dv_o} \right)^{-1} \\ \frac{dv_i}{dv_o} &= 0.5 + \frac{K_{n-L}}{2K_{n-S}} \left[ 1 - \frac{\left( V_{DD} - V_{TNL} \right)^2}{v_o^2} \right] + \frac{K_{n-L}}{K_{n-S}} \left( \frac{dV_{TNL}}{dv_o} \right) \end{split}$$

ECE 3040 - Dr. Alan Doolittle

Georgia Tech

Setting this derivative=-1 and solving for  $v_0$ :

$$\frac{dv_i}{dv_o} = 0.5 + \frac{K_{n-L}}{2K_{n-S}} \left[ 1 - \frac{(V_{DD} - V_{TNL})^2}{v_o^2} \right] = -1$$

$$v_o = \frac{(V_{DD} - V_{TNL})}{\sqrt{1 + 3\frac{(W/L)_S}{(W/L)_L}}}$$

or in our case,

$$v_o = \frac{(5-1)}{\sqrt{1+3(3.53)(3.39)}} = 0.66V$$

Plugging this back into our expression for  $v_i$ ,

$$\begin{split} v_i &= V_{TNS} + 0.5v_O + \frac{K_{n-L}}{2K_{n-S}} \left[ \frac{V_{DD} - V_{TNL}}{v_O} - 2(V_{DD} - V_{TNL}) + v_o \right] \\ v_i &= 1 + 0.5(0.66) + \frac{1}{2(3.53)(3.39)} \left[ \frac{5 - 1}{0.66} - 2(5 - 1) + 0.66 \right] = 1.97V \\ V_{IH} &= 1.97V \end{split}$$

All assumptions can be checked and verified!

Georgia Tech

Noise Margins:

$$NM_{L} = V_{IL} - V_{OL}$$

and,

$$NM_{H} = V_{OH} - V_{IH}$$

Georgia Tech

Recall that the depletion mode NMOS transistor has a threshold voltage that is negative, resulting it being on for  $v_{GS}=0$ .

Once again, to insure that  $M_S$  is sufficiently cutoff, we choose  $V_{OL} << V_{TN-S}$  or for our example where  $V_{TN-S}=1$  V,  $V_{OL}=0.25$  V. Thus, when  $v_i=V_{OL}$ ,  $M_S$  is off.

Thus, when  $M_S$  is sufficiently cutoff,  $(v_i=V_{OL} << V_{TN-S}) v_O=V_{OH}=V_{DD}$  due to the depletion load conducting for all output voltages allowing  $C_L$  to charge up to the power supply voltage. (I.e. unlike the enhancement case, the load transistor never cuts off).

Thus, the depletion load inverter allows  $V_{OH}$  to equal  $V_{DD}$ , a very nice improvement over the saturated Load case! Georgia Tech ECE 3040 - Dr. Alan Doolittle

i

i

Using  $V_{DD} = 5V$ ,  $V_{OL} = 0.25V$ ,  $V_{TN-L} = -3V$ ,  $I_{DS} = 50uA$ ,  $K_n' = 25 uA/V^2$ ,  $\gamma = 0.5\sqrt{V}$  and  $2\phi_F = 0.6V$ and noting that when  $v_i = V_{OH}$ ,  $v_O = V_{OL} = 0.25V$  means  $v_{DS-L} = V_{DD} - v_O = 4.75V$  and  $v_{GS-S} = 0 \rightarrow M_L$  is saturated, Thus,

$$DS-L = \frac{K_n}{2} \left( \frac{W}{L} \right) \Big|_L \left( v_{GS-L} - V_{TN-L} \right)^2$$

$$DS-L = \frac{K_n}{2} \left( \frac{W}{L} \right) \Big|_L \left( V_{TN-L} \right)^2$$

Inverter State: Input is High Output is Low

but due to the Body - Source voltage effect on  $M_L$ ,

$$V_{\text{TN-L}} = V_{\text{TNO}} + \gamma \left( \sqrt{v_{\text{SB}} + 2\phi_{\text{F}}} - \sqrt{2\phi_{\text{F}}} \right) \text{ or in our case,}$$

$$V_{\text{TN-L}} = -3V + 0.5\sqrt{V} \left( \sqrt{0.25V + 0.6V} - \sqrt{0.6V} \right) = -2.93V$$

Thus,

$$\left(\frac{W}{L}\right)_{L} = 0.466 = \frac{1}{2.15}$$

Georgia Tech

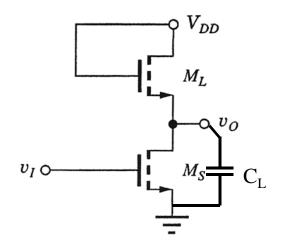

Inverter State: Input is High Output is Low

Using

$$V_{DD} = 5V$$

,  $V_{OL} = 0.25V$ ,  $V_{TN-S} = 1V$ ,

$I_{DS} = 50uA$ ,  $K_n' = 25 uA/V^2$ ,  $\gamma = 0.5\sqrt{V}$

and noting that when

$v_i = V_{OH}$ ,  $v_O = V_{OL} = 0.25V$  means  $v_{DS-S} = v_O = 0.25V$  and

$v_{GS-S} = V_{OH} = V_{DD} = 5V \rightarrow M_S$  is in the linear region,

$i_{DS} = 50\mu A = K'_n \left(\frac{W}{L}\right)\Big|_S (v_{GS-S} - V_{TN-S} - 0.5v_{DS-S})v_{DS-S}$

$50e - 6 = 25e - 6\left(\frac{W}{L}\right)\Big|_S (5 - 1 - .125)0.25$

$\left(\frac{W}{L}\right)\Big|_S = \frac{2.06}{1}$

NOTE : This is the same as in the resistive load case!

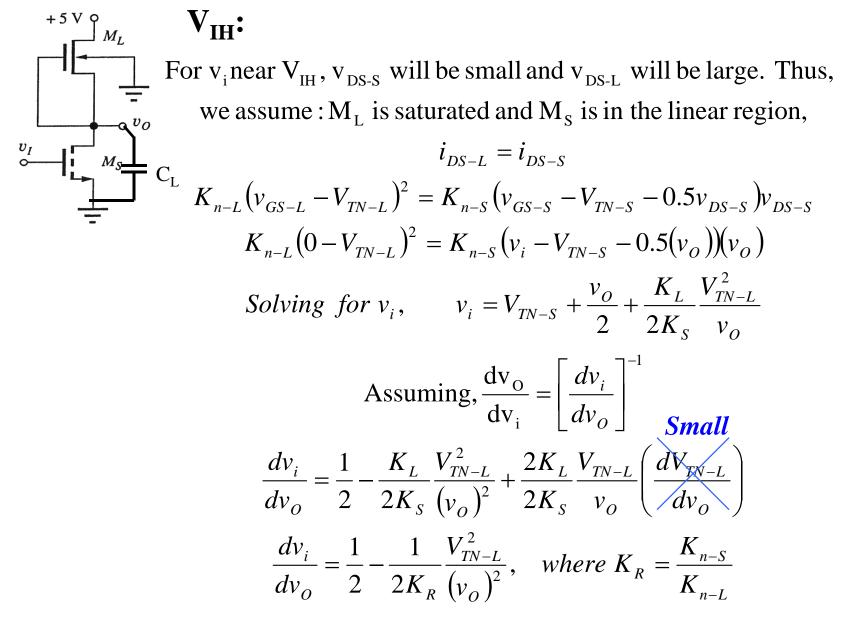

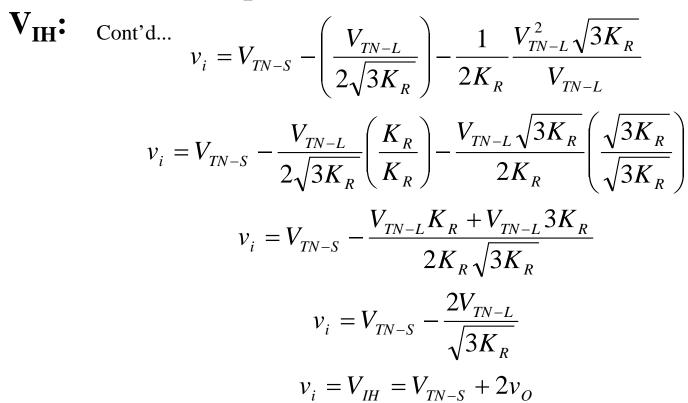

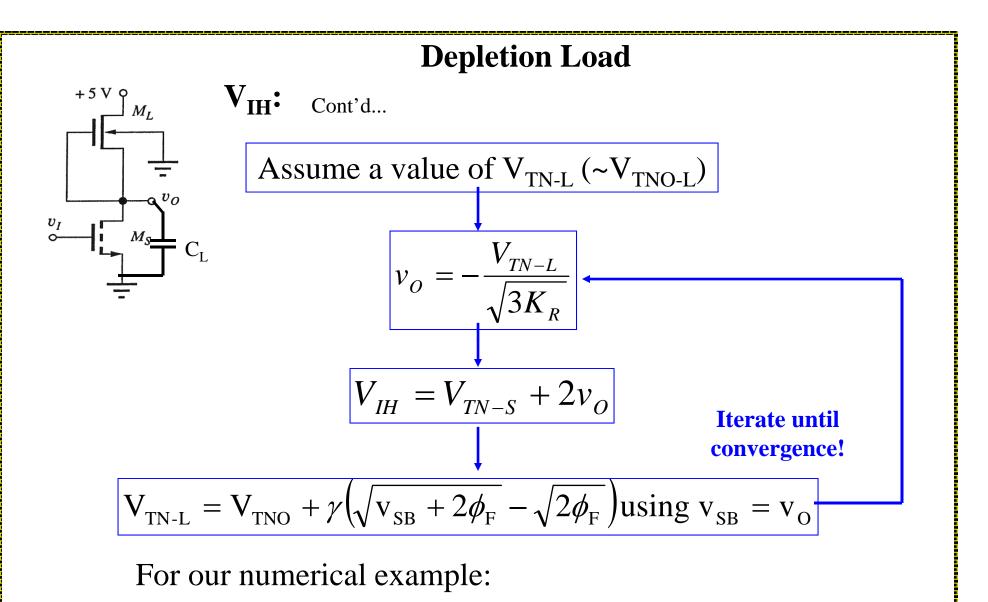

**Depletion Load**

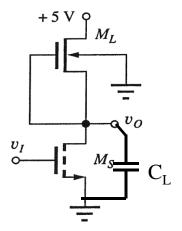

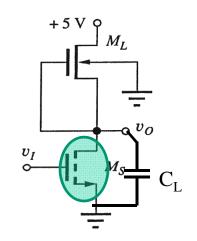

Inverter Transitional State:

Input is Low

Output is High

we assume : M<sub>s</sub> is saturated and M<sub>L</sub> is in the linear region,

$$v_{0}$$

we assume : M<sub>s</sub> is saturated and M<sub>L</sub> is in the linear region,

$v_{0}$  we assume : M<sub>s</sub> is saturated and M<sub>L</sub> is in the linear region,

$V_{0}$   $V_{0}$   $K_{n-s} (v_{GS-s} - V_{TN-s})^{2} = K_{n-L} (v_{GS-L} - V_{TN-L} - 0.5v_{DS-L}) v_{DS-L}$

$K_{n-s} (v_{i} - V_{TN-s})^{2} = K_{n-L} (0 - V_{TN-L} - 0.5(V_{DD} - v_{0}))(V_{DD} - v_{0})$

Solving for  $v_{0}$ ,

$v_{0} = V_{DD} + V_{TN-L} + \sqrt{V_{TN-L}^{2} - K_{R} (v_{i} - V_{TN-s})^{2}}$

where  $K_{R} = \frac{K_{n-S}}{K_{n-L}}$

Solving for  $v_{0}$ ,

$v_{0} = \frac{dV_{TN-L}}{dv_{i}} + \frac{1}{2} [V_{TN-L}^{2} - K_{R} (v_{i} - V_{TN-s})^{2}]^{\frac{1}{2}} [2V_{TN-L} \frac{dV_{1N-L}}{dv_{i}} - 2K_{R} (v_{i} - V_{TN-s})]$

$\frac{dv_{0}}{dv_{i}} = \frac{-K_{R} (v_{i} - V_{TN-s})}{\sqrt{V_{TN-L}^{2} - K_{R} (v_{i} - V_{TN-s})^{2}}$

ECE 3040 - Dr. Atan Depolitie

For our numerical example:  $M_{s} = C_{L}$   $V_{TN-L} = -2.23 V$  (>-3V)  $V_{IL} = 1.50 V$

v<sub>o</sub>=4.74 V

Also, our assumptions regarding transistor operation conditions are correct.

Georgia Tech

ECE 3040 - Dr. Alan Doolittle

Georgia Tech

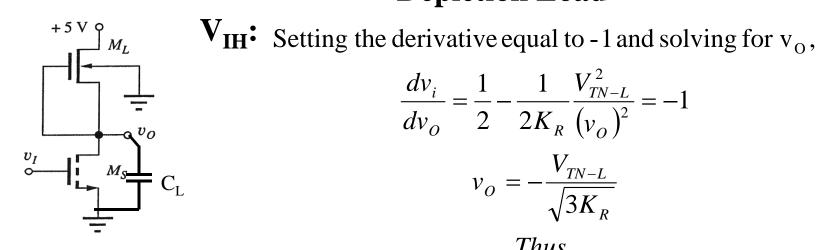

# **Depletion Load**

Inverter Transitional State: Input is High Output is Low

Thus,

Cont'd... ECE 3040 - Dr. Alan Doolittle

### **Depletion Load**

ECE 3040 - Dr. Alan Doolittle

$$V_{\text{TN-L}}$$

=-2.80 V,  $V_{\text{IH}}$ =2.53 V,  $v_{\text{O}}$ =0.77 V

Also, our assumptions regarding transistor operation conditions are correct.

Georgia Tech

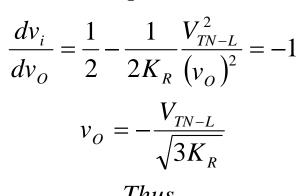

#### **Depletion Load**

VTC

Georgia Tech

**Georgia Tech**

# **Depletion Load**

The Depletion Load NMOS gate...

... takes up much less area, leading to higher density (more complex and faster) circuitry.

... has a  $V_{OH} = V_{DD}$

...switches faster leading to higher frequency operation.

... dominated microprocessor design until "CMOS" or Combination-MOS replaced it.

**Georgia Tech**

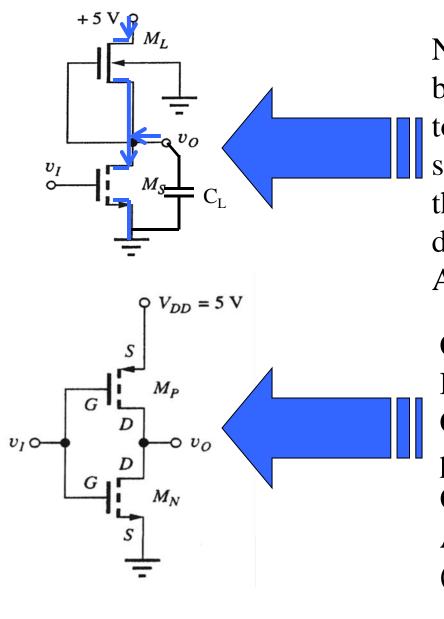

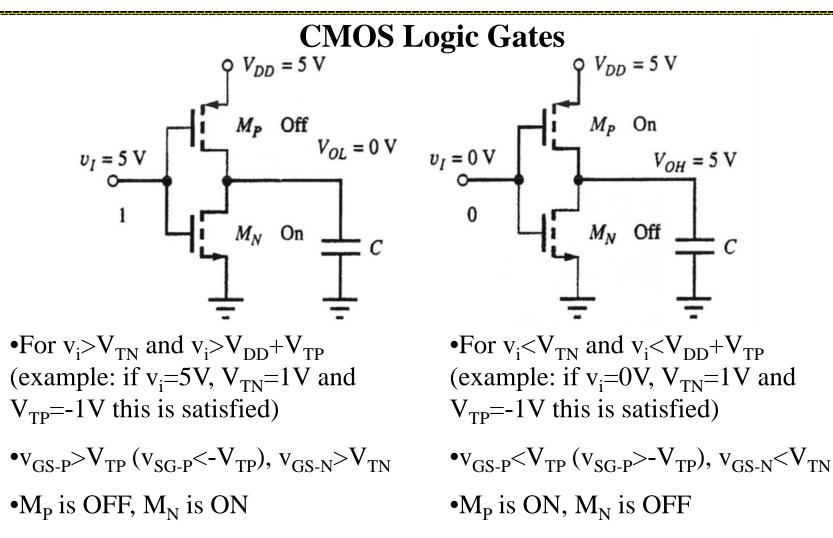

NMOS Logic Gates "waste" power by having a current flow from  $V_{DD}$ to ground during the "0" output state. All we really need during this state is a current path to discharge  $C_L$ . Analogous to a Class A out put stage.

CMOS Logic Gates eliminate this DC or "Static" power dissipation. CMOS logic gates only dissipate power during a switching event. Once in a state, no power is used. Analogous to a class B output stage (push pull).

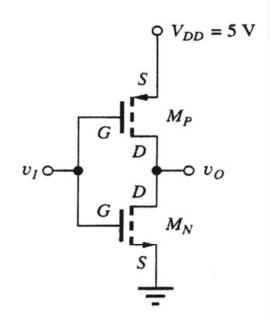

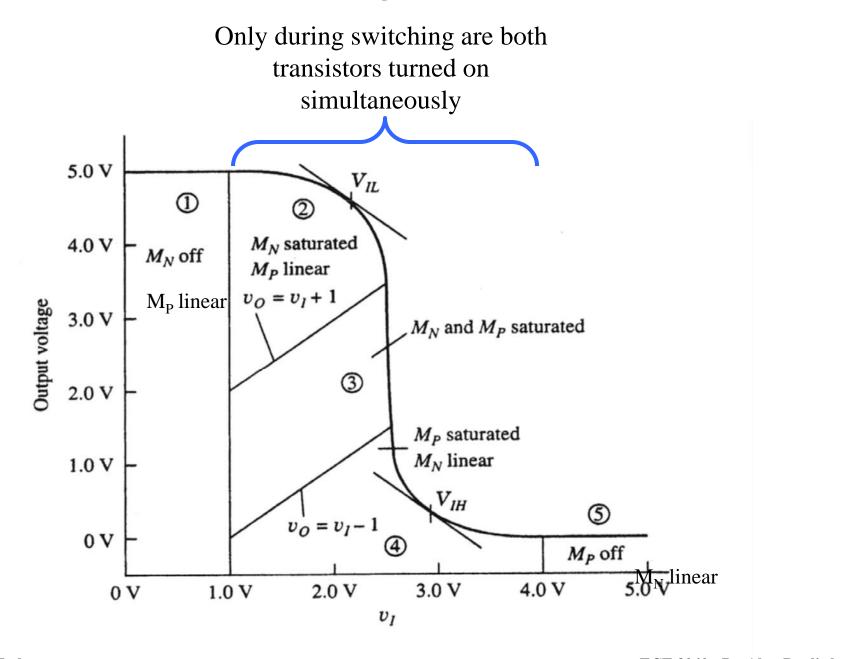

•CMOS Inverter uses one NMOS and 1 PMOS transistor.

•Each Transistor is design to have  $V_{TN}$ =- $V_{TP}$  (recall for PMOS,  $V_{TP}$ <0)

•Since the Body can be connected to source for the NMOS and VDD for the PMOS, there is no problem with the body effect *FOR THE CMOS INVERTER (ONLY)*

Georgia Tech

- •Load Capacitor discharges all the way down to ground

- •Load Capacitor charges all the way up to  $V_{\text{DD}}.$

Thus,

$$V_{OL}=0V$$

and  $V_{OH}=V_{DD}$

and there is <u>NO STEADY\_STATE DC CURRENT FLOW</u> ECE 3040 - Dr. Alan Doolittle

Georgia Tech

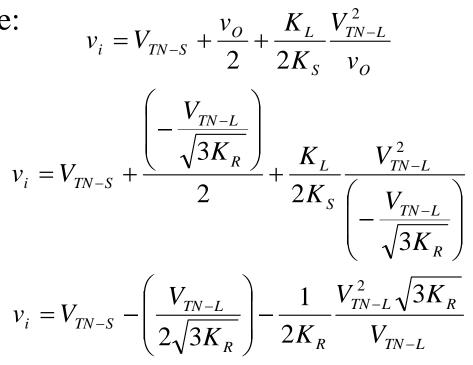

# V<sub>IH</sub>:

For  $v_i \sim V_{IH}$ ,  $v_{DS-P}$  is large and  $v_{DS-N}$  is small implying  $M_P$  is saturated and  $M_N$  is linear

$$i_{DS-N} = i_{DS-P}$$

$$K_{n}(v_{GS-N} - V_{TN} - 0.5V_{DS-N})V_{DS-N} = \frac{Kp}{2}(v_{SG-P} + V_{TP})^{2}$$

$$K_{n}(v_{i} - V_{TN} - 0.5v_{o})v_{o} = \frac{Kp}{2}((V_{DD} - v_{i}) + V_{TP})^{2}$$

Solving for v<sub>o</sub>,

$$K_{n}(v_{i} - V_{TN} - 0.5v_{o})v_{o} = \frac{Kp}{2}((V_{DD} - v_{i}) + V_{TP})^{2}$$

$$K_{n}(v_{i} - V_{TN} - 0.5v_{o})v_{o} = \frac{Kp}{2}((V_{DD} - v_{i}) + V_{TP})^{2}$$

$$v_{O} = v_{i} - V_{TN} \pm \sqrt{(v_{i} - V_{TN})^{2} - \frac{(V_{DD} - v_{i} + V_{TP})^{2}}{K_{R}}}$$

where  $K_{R} = \frac{K_{R}}{K_{P}}$

As before, taking he derivative,  $\frac{dv_o}{dv_i}$  and setting this equal to -1 and solving for  $v_i$ ,

$$\mathbf{V}_{\text{IH}} = \mathbf{v}_{\text{i}} \bigg|_{\frac{dv_{O}}{dv_{i}} = -1} = \frac{2\mathbf{K}_{\text{R}} (\mathbf{V}_{\text{DD}} - \mathbf{V}_{\text{TN}} + \mathbf{V}_{\text{TP}})}{(K_{R} - 1)\sqrt{1 + 3K_{R}}} - \frac{(\mathbf{V}_{\text{DD}} - \mathbf{K}_{\text{R}} \mathbf{V}_{\text{TN}} + \mathbf{V}_{\text{TP}})}{(K_{R} - 1)}$$

ECE 3040 - Dr. Alan Doolittle

V<sub>IH</sub> (cont'd):

For a very useful case where  $K_n = K_p (K_R = 1)$

Do not use this equation without mathematical manipulation to eliminate  $(K_R - 1)$  terms in denominator

$$V_{\rm IH} = V_{\rm i} \bigg|_{\frac{dv_o}{dv_i} = -1} = \frac{2K_{\rm R} (V_{\rm DD} - V_{\rm TN} + V_{\rm TP})}{(K_{\rm R} - 1)\sqrt{1 + 3K_{\rm R}}} - \frac{(V_{\rm DD} - K_{\rm R} V_{\rm TN} + V_{\rm TP})}{(K_{\rm R} - 1)}$$

Instead, go back to,

$$v_{O} = v_{i} - V_{TN} \pm \sqrt{(v_{i} - V_{TN})^{2} - \frac{(V_{DD} - v_{i} + V_{TP})^{2}}{K_{R}}}$$

where  $K_{R} = \frac{K_{n}}{K_{p}} = 1$

As before, taking he derivative,  $\frac{dv_o}{dv_i}$  and setting this equal to -1 and solving for  $v_i$ ,

$$V_{IH} = v_i \bigg|_{\frac{dv_o}{dv_i} = -1} = \frac{(5V_{DD} + 3V_{TN} + 5V_{TP})}{8} \quad For \ K_R = \frac{K_n}{K_p} = 1$$

Georgia Tech

V<sub>IL</sub>:

For  $v_i \sim V_{IL}$ ,  $v_O$  is large. Thus,  $v_{DS-P}$  is small and  $v_{DS-N}$  is large implying  $M_P$  is linear and  $M_N$  is saturated Inverter Transitional State:

- Input is Low

- $i_{DS-P} = i_{DS-N}$  Output is High

$$K_{p} (v_{SG-P} + V_{TP} - 0.5V_{SD-P}) V_{SD-P} = \frac{K_{n}}{2} (v_{GS-N} - V_{TN})^{2}$$

$$K_{p} ((V_{DD} - v_{i}) + V_{TP} - 0.5(V_{DD} - v_{o})) (V_{DD} - v_{o}) = \frac{K_{n}}{2} (v_{i} - V_{TN})^{2}$$

Again, solving for  $v_0$ , taking he derivative,  $\frac{dv_0}{dv_i}$  and setting this equal

to -1 and solving for  $v_i$ ,

$$\mathbf{V}_{\rm IL} = \mathbf{v}_{\rm i} \bigg|_{\frac{dv_O}{dv_i} = -1} = \frac{2\sqrt{K_{\rm R}} \left( V_{\rm DD} - V_{\rm TN} + V_{\rm TP} \right)}{\left( K_{\rm R} - 1 \right) \sqrt{K_{\rm R} + 3}} - \frac{\left( V_{\rm DD} - K_{\rm R} V_{\rm TN} + V_{\rm TP} \right)}{\left( K_{\rm R} - 1 \right)}$$

ECE 3040 - Dr. Alan Doolittle

V<sub>IL</sub> (cont'd):

For a very useful case where  $K_n = K_p (K_R = 1)$

$$V_{IL} = v_{i} \bigg|_{\frac{dv_{o}}{dv_{i}} = -1} = \frac{2\sqrt{K_{R}} (V_{DD} - V_{TN} + V_{TP})}{(K_{R} - 1)\sqrt{K_{R} + 3}} - \frac{(V_{DD} - K_{R} V_{TN} + V_{TP})}{(K_{R} - 1)}$$

$$V_{IL} = v_{i} \bigg|_{\frac{dv_{o}}{dv_{i}} = -1} = \frac{(3V_{DD} + 5V_{TN} + 3V_{TP})}{8} \quad for \ K_{R} = \frac{K_{n}}{K_{P}} = 1$$

As always, we can calculate the appropriate noise margins.

Georgia Tech

Example: Calculate the noise margins for a logic family with  $V_{DD}$ =3.3V,  $V_{TN}$ =1V,  $V_{TP}$ = -0.75V and  $K_R$ =1:

$$V_{OH} = 3.3V$$

$$V_{OL} = 0V$$

$$V_{IH} = \frac{(5V_{DD} + 3V_{TN} + 5V_{TP})}{8} = \frac{(5(3.3) + 3(0.75) + 5(-0.75))}{8} = 1.86V$$

$$V_{IL} = \frac{(3V_{DD} + 5V_{TN} + 3V_{TP})}{9} = \frac{(3(3.3) + 5(0.75) + 3(-0.75))}{9} = 1.43V$$

8

$$NM_{H} = V_{OH} - V_{IH} = V_{DD} - V_{IH} = 1.43V$$

$$NM_{L} = V_{IL} - V_{OL} = V_{IL} = 1.43V$$

8

ECE 3040 - Dr. Alan Doolittle

Dynamic Response of a CMOS Inverter:

For the case when  $V_{TN}$ =- $V_{TP}$  and  $K_R$ =1, the transistors are said to be "electrically equivalent" meaning they have identically "opposite" current-voltage characteristics ("on resistance" in the linear state is the same, the voltage turn on points are symmetric etc...).

In this case, the turn on transient and the turn off transient are identical (charging of  $C_L$  is through a resistor,  $R_{on-PMOS}$  and discharging of  $C_L$  is through a resistor,  $R_{on-NMOS}$  where  $R_{on-PMOS} = R_{on-NMOS}$ )

$$\mathbf{R}_{\text{on-NMOS}} = \frac{1}{\mathbf{K}_{n} (\mathbf{V}_{\text{DD}} - \mathbf{V}_{\text{TN}})} \quad and \quad \mathbf{R}_{\text{on-PMOS}} = \frac{1}{\mathbf{K}_{p} (\mathbf{V}_{\text{DD}} + \mathbf{V}_{\text{TP}})}$$

Georgia Tech

The charging time is related to the "RC time constant" of this resistance and the load capacitor. Detailed analysis indicates a slight elongation of the time constant (due to the resistance of the channel changing during the switching cycle) leading to,

$\tau_{\rm PHL} = 1.29 R_{\rm on-NMOS} C_{\rm L}$  and  $\tau_{\rm PLH} = 1.29 R_{\rm on-PMOS} C_{\rm L}$ It can also be found that,

$$t_{\rm f} = 2\tau_{\rm PHL}$$

and  $t_{\rm r} = 2\tau_{\rm PLH}$

For  $K_R=1$ , these are equal greatly simplifying timing designs in complex circuits.

$$\tau_{\rm P} = \frac{\tau_{\rm PHL} + \tau_{\rm PLH}}{2} = \tau_{\rm PLH} = \tau_{\rm PHL}$$

ECE 3040 - Dr. Alan Doolittle

Power Considerations:

Since power is only dissipated during a switching event, it can be shown that for a CMOS inverter the power dissipated is,

$$P_D = C_L V_{DD}^2 f$$

Where f is the switching frequency (assuming a 50% duty cycle).

Note that for DC, f=0, P<sub>D</sub>=0 as expected

Georgia Tech

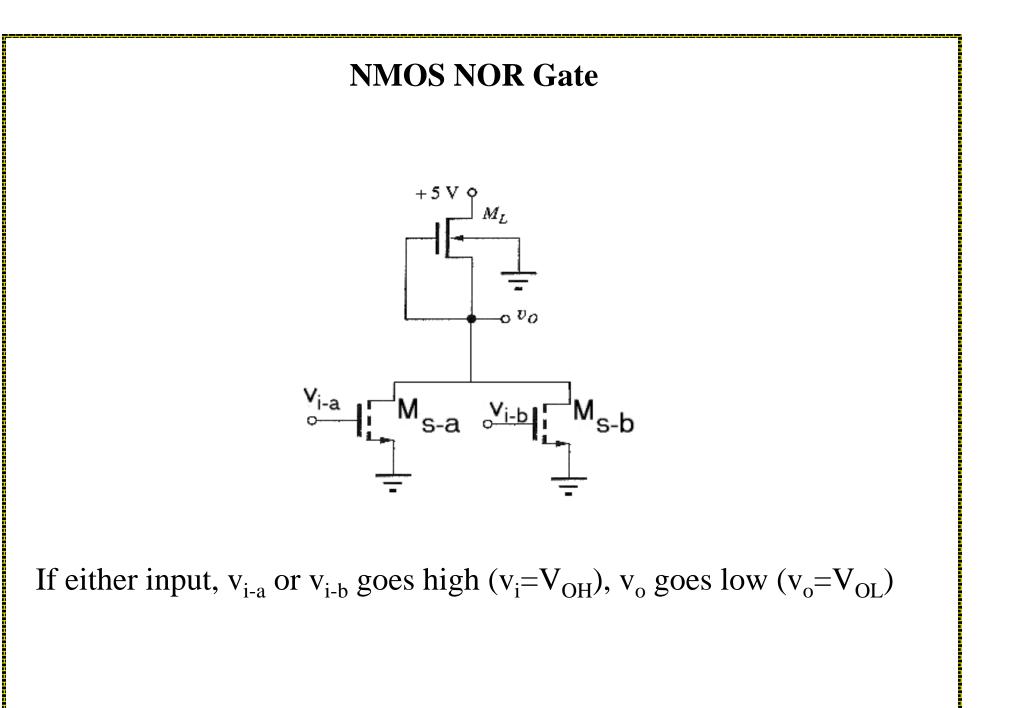

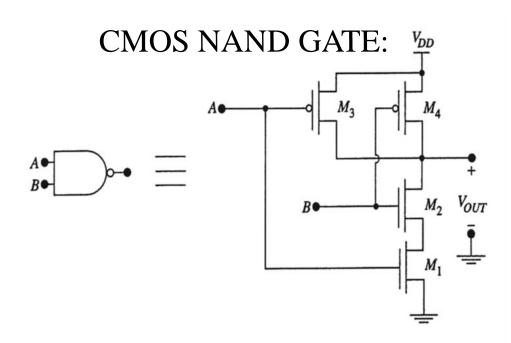

#### CMOS Logic Gates CMOS NOR GATE: $V_{DD}$ $M_4$ $M_4$

•If both A and B are low,  $M_1$  and  $M_2$  are off, and  $M_3$  and  $M_4$  are on allowing  $V_{out}$  to be pulled high

•If either A, B or both are high,  $M_1$  or  $M_2$  or both are on and  $M_3$ , or  $M_4$  or both are off allowing  $V_{out}$  to be pulled low

•Note that the body effect would modify our design (W/L) of  $M_3$

Georgia Tech

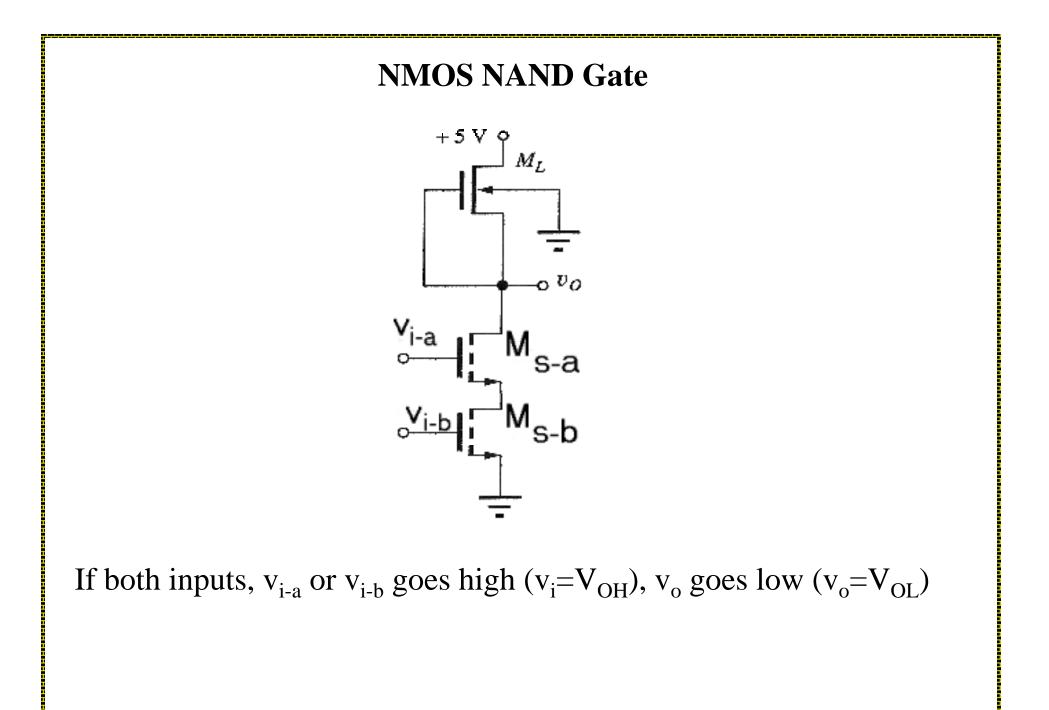

•If both A and B are high,  $M_1$  and  $M_2$  are on, and  $M_3$  and  $M_4$  are off allowing  $V_{out}$  to be pulled low

•If either A, B or both are low,  $M_1$  or  $M_2$  or both are off and  $M_3$ , or  $M_4$  or both are on allowing  $V_{out}$  to be pulled low

•Note that the body effect would modify our design (W/L) of  $M_2$

Georgia Tech