# LECTURE 200 – CASCODE OP AMPS II (READING: GHLM – 443-453, AH – 293-309)

## **Objective**

The objective of this presentation is:

- 1.) Develop cascode op amp architectures

- 2.) Show how to design with the cascode op amps

## **Outline**

- Op amps with cascoding in the first stage

- Op amps with cascoding in the second stage

- Folded cascode op amp

- Summary

ECE 6412 - Analog Integrated Circuit Design - II

© P.E. Allen - 2002

Page 200-2

Lecture 200 – Cascode Op Amps - II (2/18/02)

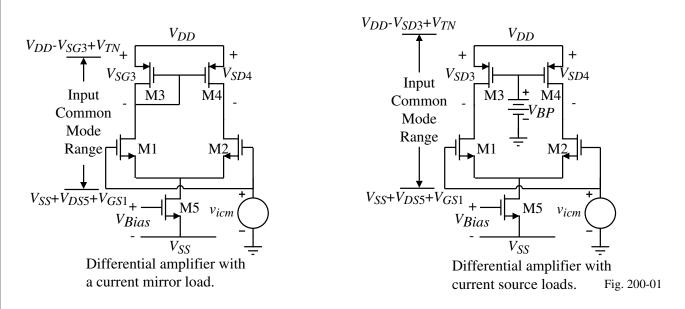

#### Input Common Mode Range for Two Types of Differential Amplifier Loads

In order to improve the ICMR, it is desirable to use current source (sink) loads without losing half the gain.

The resulting solution is the *folded* cascode op amp.

Page 200-3

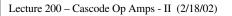

## **The Folded Cascode Op Amp**

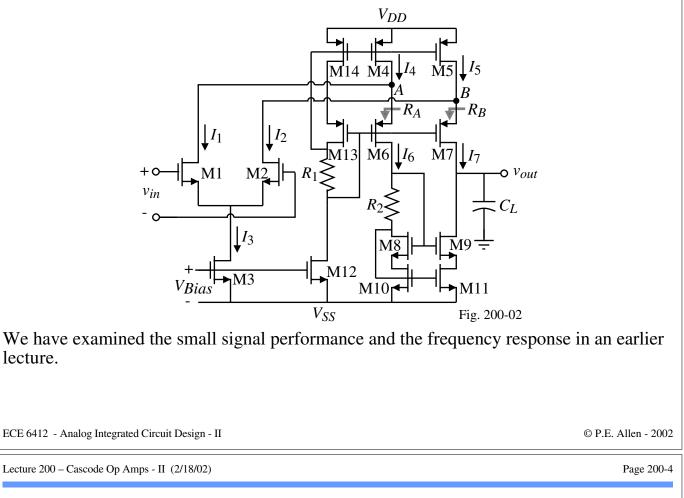

## PSRR of the Folded Cascode Op Amp

Consider the following circuit used to model the PSRR-:

This model assumes that gate, source and drain of M11 and the gate and source of M9 all vary with  $V_{SS}$ .

We shall examine  $V_{out}/V_{ss}$  rather than *PSRR*-. (Small  $V_{out}/V_{ss}$  will lead to large *PSRR*-.) The transfer function of  $V_{out}/V_{ss}$  can be found as

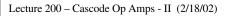

$$\frac{V_{out}}{V_{ss}} \approx \frac{sC_{gd9}R_{out}}{sC_{out}R_{out}+1} \quad \text{for } C_{gd9} < C_{out}$$

The approximate PSRR- is sketched on the next page.

ECE 6412 - Analog Integrated Circuit Design - II

#### Frequency Response of the PSRR- of the Folded Cascode Op Amp

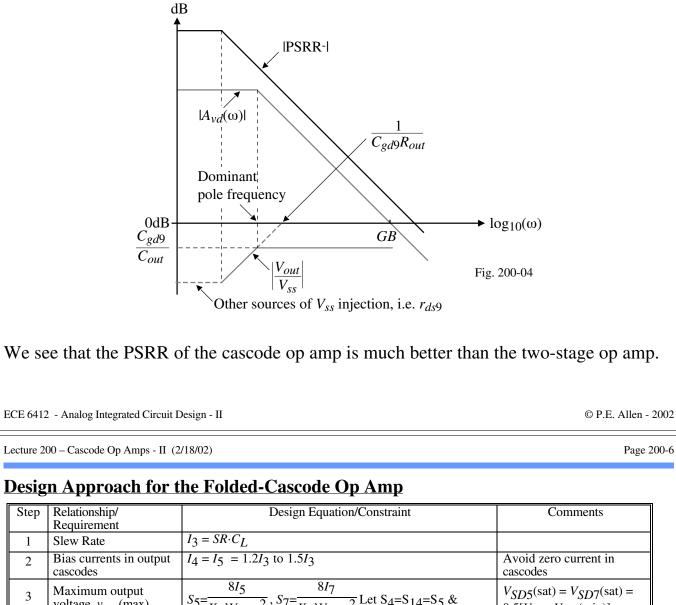

| 3  | Maximum output<br>voltage, v <sub>out</sub> (max) | $S_5 = \frac{8I_5}{K_P'V_{SD5}^2}$ , $S_7 = \frac{8I_7}{K_P'V_{SD7}^2}$ Let $S_4 = S_{14} = S_5$ & $S_{13} = S_6 = S_7$              | $V_{SD5}(\text{sat}) = V_{SD7}(\text{sat}) = 0.5[V_{DD}-V_{out}(\text{min})]$      |

|----|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

|    |                                                   |                                                                                                                                      |                                                                                    |

| 4  | Minimum output<br>voltage, v <sub>out</sub> (min) | $S_{11} = \frac{8I_{11}}{K_N V_{DS11}^2}, S_9 = \frac{8I_9}{K_N V_{DS9}^2}$ Let $S_{10} = S_{11}$ &                                  | $V_{DS9}(\text{sat}) = V_{DS11}(\text{sat}) = 0.5(V_{out}(\text{min}) -  V_{SS} )$ |

|    |                                                   | S <sub>8</sub> =S <sub>9</sub>                                                                                                       |                                                                                    |

| 5  | Self-bias cascode                                 | $R_1 = V_{SD14}(\text{sat})/I_{14}$ and $R_2 = V_{DS8}(\text{sat})/I_6$                                                              |                                                                                    |

| 6  | $GB = \frac{g_{m1}}{C_L}$                         | $S_1 = S_2 = \frac{g_{m1}^2}{K_N I_3} = \frac{GB^2 C_L^2}{K_N I_3}$                                                                  |                                                                                    |

| 7  | Minimum input CM                                  | $S_{3} = \frac{2I_{3}}{K_{N'} \left( V_{in}(\text{min}) - V_{SS} - \sqrt{\frac{I_{3}}{K_{N'} S_{1}}} - V_{T1} \right)^{2}}$          |                                                                                    |

| 8  | Maximum input CM                                  | $S_4 = S_5 = \frac{2I_4}{K_P'(V_{DD} - V_{in}(\max) + V_{T1})^2}$                                                                    | S <sub>4</sub> and S <sub>5</sub> must meet or<br>exceed the value in step 3       |

| 9  | Differential Voltage<br>Gain                      | $\frac{v_{out}}{v_{in}} = \left(\frac{g_{m1}}{2} + \frac{g_{m2}}{2(1+k)}\right)R_{out} = \left(\frac{2+k}{2+2k}\right)g_{mI}R_{out}$ |                                                                                    |

| 10 | Power dissipation                                 | $P_{diss} = (V_{DD} - V_{SS})(I_3 + I_{12} + I_{10} + I_{11})$                                                                       |                                                                                    |

ECE 6412 - Analog Integrated Circuit Design - II

#### Lecture 200 – Cascode Op Amps - II (2/18/02)

#### **Example 3 - Design of a Folded-Cascode Op Amp**

Follow the procedure given to design the folded-cascode op amp when the slew rate is  $10V/\mu s$ , the load capacitor is 10pF, the maximum and minimum output voltages are  $\pm 2V$  for  $\pm 2.5V$  power supplies, the *GB* is 10MHz, the minimum input common mode voltage is -1.5V and the maximum input common mode voltage is 2.5V. The differential voltage gain should be greater than 5,000V/V and the power dissipation should be less than 5mW. Use channel lengths of 1 $\mu m$ .

**Solution**

Following the approach outlined above we obtain the following results.

$$I_3 = SR \cdot C_L = 10 \times 10^6 \cdot 10^{-11} = 100 \mu A$$

Select  $I_4 = I_5 = 125 \mu A$ .

Next, we see that the value of  $0.5(V_{DD}-V_{out}(\max))$  is 0.5V/2 or 0.25V. Thus,

$$S_4 = S_5 = S_{14} = \frac{2 \cdot 125 \mu A}{50 \mu A / V^2 \cdot (0.25 V)^2} = \frac{2 \cdot 125 \cdot 16}{50} = 80$$

and assuming worst case currents in M6 and M7 gives,

$$S_6 = S_7 = S_{13} = \frac{2 \cdot 125 \mu A}{50 \mu A / V^2 (0.25 V)^2} = \frac{2 \cdot 125 \cdot 16}{50} = 80$$

The value of  $0.5(V_{out}(min)-|V_{SS}|)$  is also 0.25V which gives the value of  $S_8$ ,  $S_9$ ,  $S_{10}$  and  $S_{11}$

as

$$S_8 = S_9 = S_{10} = S_{11} = \frac{2 \cdot I_8}{K_N \cdot V_{DS8}^2} = \frac{2 \cdot 125}{110 \cdot (0.25)^2} = 36.36$$

ECE 6412  $\,$  - Analog Integrated Circuit Design - II

Lecture 200 – Cascode Op Amps - II (2/18/02)

#### **Example 3 - Continued**

The value of  $R_1$  and  $R_2$  is equal to 0.25V/125µA or 2k $\Omega$ . In step 6, the value of *GB* gives  $S_1$  and  $S_2$  as

$$S_1 = S_2 = \frac{GB^2 \cdot C_L^2}{K_N \cdot I_3} = \frac{(20\pi x \cdot 10^6)^2 (10^{-11})^2}{110x \cdot 10^{-6} \cdot 100x \cdot 10^{-6}} = 35.9$$

The minimum input common mode voltage defines  $S_3$  as

$$S_{3} = \frac{2I_{3}}{K_{N}' \left(V_{in}(\text{min}) - V_{SS} - \sqrt{\frac{I_{3}}{K_{N}'S_{1}}} - V_{T1}\right)^{2}} = \frac{200 \times 10^{-6}}{110 \times 10^{-6} \left(-1.5 + 2.5 - \sqrt{\frac{100}{110 \cdot 35.9}} - 0.75\right)^{2}} = 20$$

We need to check that the values of  $S_4$  and  $S_5$  are large enough to satisfy the maximum input common mode voltage. The maximum input common mode voltage of 2.5 requires

$$S_4 = S_5 \ge \frac{2I_4}{K_P'[V_{DD} - V_{in}(\max) + V_{T1}]^2} = \frac{2 \cdot 125 \mu A}{50 \times 10^{-6} \mu A / V^2 [0.7V]^2} = 10.2$$

which is much less than 80. In fact, with  $S_4 = S_5 = 80$ , the maximum input common mode voltage is 3V. Finally,  $S_{12}$ , is given as

$$S_{12} = \frac{125}{100} S_3 = 25$$

The power dissipation is found to be

$$P_{diss} = 5V(125\mu A + 125\mu A + 125\mu A) = 1.875mW$$

ECE 6412 - Analog Integrated Circuit Design - II

© P.E. Allen - 2002

© P.E. Allen - 2002

Page 200-8

The small-signal voltage gain requires the following values to evaluate:

$$\begin{split} s_4, s_5, s_{13}, s_{14}: & g_m = \sqrt{2 \cdot 125 \cdot 50 \cdot 80} = 1000 \mu \text{S} \quad \text{and} \quad g_{ds} = 125 \times 10^{-6} \cdot 0.05 = 6.25 \mu \text{S} \\ s_6, s_7: & g_m = \sqrt{2 \cdot 75 \cdot 50 \cdot 80} = 774.6 \mu \text{S} \quad \text{and} \quad g_{ds} = 75 \times 10^{-6} \cdot 0.05 = 3.75 \mu \text{S} \\ s_8, s_9, s_{10}, s_{11}: & g_m = \sqrt{2 \cdot 75 \cdot 110 \cdot 36.36} = 774.6 \mu \text{S} \quad \text{and} \quad g_{ds} = 75 \times 10^{-6} \cdot 0.04 = 3 \mu \text{S} \\ s_1, s_2: & g_{mI} = \sqrt{2 \cdot 50 \cdot 110 \cdot 35.9} = 628 \mu \text{S} \quad \text{and} \quad g_{ds} = 50 \times 10^{-6} (0.04) = 2 \mu \text{S} \end{split}$$

Thus,

$$R_{II} \approx g_{m9} r_{ds9} r_{ds11} = (774.6\mu\text{S}) \left(\frac{1}{3\mu\text{S}}\right) \left(\frac{1}{3\mu\text{S}}\right) = 86.07\text{M}\Omega$$

$$R_{out} \approx 86.07\text{M}\Omega ||(774.6\mu\text{S}) \left(\frac{1}{3.75\mu\text{S}}\right) \left(\frac{1}{2\mu\text{S}+6.25\mu\text{S}}\right) = 19.40\text{M}\Omega$$

$$k = \frac{R_{II}(g_{ds2}+g_{ds4})}{g_{m7} r_{ds7}} = \frac{86.07\text{M}\Omega(2\mu\text{S}+6.25\mu\text{S})(3.75\mu\text{S})}{774.6\mu\text{S}} = 3.4375$$

The small-signal, differential-input, voltage gain is

$$A_{vd} = \left(\frac{2+k}{2+2k}\right) g_{ml}R_{out} = \left(\frac{2+3.4375}{2+6.875}\right) 0.628 \times 10^{-3} \cdot 19.40 \times 10^{6} = 7,464 \text{ V/V}$$

The gain is larger than required by the specifications which should be okay.

ECE 6412 - Analog Integrated Circuit Design - II

Lecture 200 – Cascode Op Amps - II (2/18/02)

## **Comments on Folded Cascode Op Amps**

- Good PSRR

- Good ICMR

- Self compensated

- Can cascade an output stage to get extremely high gain with lower output resistance (use Miller compensation in this case)

- Need first stage gain for good noise performance

- Widely used in telecommunication circuits where large dynamic range is required

© P.E. Allen - 2002

Page 200-10

Lecture 200 - Cascode Op Amps - II (2/18/02)

Page 200-11

# **SUMMARY**

- Cascode op amps offer an alternate architecture to the two-stage op amp

- The cascode op amp is typically self-compensating

- The cascode op amp generally has better PSRR

ECE 6412 - Analog Integrated Circuit Design - II

© P.E. Allen - 2002