# Fast & Efficient Hysteretic Power Supplies for IoT Microsensors: Analysis & Design with Insight

Tianyu Chang

School of Electrical and Computer Engineering

Georgia Institute of Technology

Atlanta, U.S.A.

tchang78@gatech.edu

Gabriel A. Rincón-Mora

School of Electrical and Computer Engineering

Georgia Institute of Technology

Atlanta, U.S.A.

Rincon-Mora@gatech.edu

Abstract—Integrating and conforming emerging wireless IoT microsensors into tiny form factors is challenging in many ways. To conserve energy, for example, the system should idle whenever possible, activating functional blocks on demand only. Internal power circuits must therefore supply and cut-off power quickly. In the interim, as these react, capacitors supply and sink the mismatch in power. The low capacitance that small capacitors afford, however, cannot supply or sink much power for long. Hysteretic power supplies are appealing in this respect because they respond quickly. But how fast and reliably they respond depends on design, which hinges on understanding. This paper uses and develops insight to explain and analyze the feedback dynamics and stability requirements of hysteretic current-mode dc-dc switched-inductor converters, which are largely abstract and algebraic in literature today. Moreover, this paper also outlines and analyzes possible practical design issues related to IC implementations. To this end, the paper derives accurate and insightful expressions, uses and applies them to a design, and validates them with SPICE simulations.

Keywords—Hysteretic, switched inductor, dc-dc, power supplies, analysis, design, feedback control, stability, relaxation oscillator, load transient, bandwidth, voltage regulators.

## I. POWER SUPPLIES FOR IOT MICROSENSORS

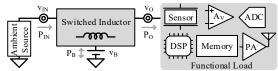

Internet-of-Things (IoT) wireless microsensors can help increase security, convenience, and quality-of-life of our society [1–5]. To save energy, wireless IoT sensors idle mostly, and only execute sensing and transmitting tasks on demand. So, the currents such sensors draw from power supplies soar drastically when they change from idle to full-power mode in microseconds [6–8]. This challenges the power supply in Fig. 1 to respond quickly to any load-dump events.

Fig. 1. An ambient-sourced switched-inductor power supply.

Secondly, since wireless IoT sensors idle mostly, they mostly present as very light loads as seen by the power supplies. This challenges a power supply's controller to consume very low quiescent power  $P_Q$  to improve light-load efficiency [9–11].

These challenges make hysteretic switched-inductor (SL) power supplies especially appealing, since hysteretic control is

fast [9], and may require as little as only one comparator (as this paper will later show), which leads to very little P<sub>O</sub>.

Unfortunately, state-of-the-art (SoA) analyses for hysteretic power supplies are largely abstract and algebraic [12–19]. Moreover, some SoA analyses are established on case-by-case bases [20–21], which means it is usually difficult to extend the same analysis to different converter and control architectures. Lastly, SoA analyses often exclude practical issues in integrated circuit (IC) implementation such as hysteretic comparator propagation delay  $t_P$ , offset  $v_{OS}$ , and load regulation [12–21].

This work, on the contrary, presents an accurate & insightful analysis on hysteretic current-mode SL dc-dc power supplies. This paper provides expressions on inductor and capacitor selection, and expressions on feedback control design. This proposed analysis can be readily extended to different hysteretic control schemes. It also incorporates t<sub>P</sub>, predicts v<sub>OS</sub> and load regulation, which is crucial for practical IC implementations.

#### II. HYSTERETIC CURRENT MODE CONTROL

## A. Hysteretic Current Loop

<u>Current Mode</u>: Current mode controls inductor current  $i_L$  by the error voltage, so that  $i_L$  behaves like a transconductor  $A_G$  which is not inductive. Because there is no inductive effect, current mode control removes the complex pole  $p_{LC}$  created by  $L_X$  and  $C_O$ . Hysteretic control sets  $i_L$  using the error voltage and removes its inductive effect. Thus, hysteretic control is current mode. The remaining of this section explains how hysteretic control sets  $i_L$  and how it could be modeled as an  $A_G$ .

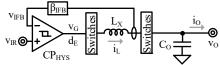

Oscillator: A hysteretic loop is a relaxation oscillator. Current sensor  $\beta_{IFB}$  in Fig. 2 senses and translates  $i_L$  into voltage  $v_{IFB}$ . Hysteretic comparator  $CP_{HYS}$  generates gate-drive signal  $v_G$  (active-high in Fig. 3) with duty cycle  $d_E$  that energizes and drains  $L_X$  periodically. During energize time  $t_E$  in Fig. 3,  $CP_{HYS}$  waits until  $i_L$  slews up and  $v_{IFB}$  reaches the higher hysteretic bound  $v_{T(HI)}$ . Once  $v_{IFB}$  reaches  $v_{T(HI)}$ ,  $CP_{HYS}$  trips so the SL drains  $i_L$  into  $v_O$ . During drain time  $t_D$ ,  $CP_{HYS}$  relaxes as  $i_L$  slews down, until  $v_{IFB}$  hits the lower hysteretic bound  $v_{T(LO)}$ .

Then,  $CP_{HYS}$  trips again so the SL energizes  $i_L$  again and  $v_{IFB}$  once more slews toward  $v_{T(HI)}$ .  $v_{IFB}$ , therefore, oscillates between  $v_{T(LO)}$  and  $v_{T(HI)}$ . Hysteretic window  $\Delta v_{HYS}$  limits the amplitude of  $v_{IFB}$  oscillation. This achieves Automatic Gain Control and regulates the oscillator's large-signal positive

feedback gain to 1 [31]. As a result, the oscillation is stable. Thus,  $v_{IFB}$ 's  $1/\beta_{IFB}$  translation  $i_L$ , also oscillates stably. In ideal scenarios,  $v_{IR}$  in Fig. 2 sets  $i_{L(AVG)}$ , and  $\Delta v_{HYS}$  sets  $\Delta i_L$ .

Fig. 2. Hysteretic relaxation oscillator.

Simply put, the hysteretic oscillator forces  $L_X$  to conduct an  $i_{L(AVG)}$  that is a  $1/\beta_{IFB}$  translation of  $v_{IR}$ . So, forced by the hysteretic oscillator,  $i_L$  behaves likes a transconductanor  $A_G = 1/\beta_{IFB}$ . Thus, hysteretic control a type of current-mode control.

Fig. 3. Simulated hysteretic waveforms without delays.

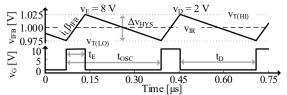

Offset: Practical comparators have propagation delay  $t_P$  [22–23]. As Fig. 4 shows,  $CP_{HYS}$  trips a rising delay  $t_P$  after  $v_{IFB}$  hits  $v_{T(HI)}$ .  $CP_{HYS}$  also trips a falling delay  $t_P$  after  $v_{IFB}$  hits  $v_{T(LO)}$ .  $t_P$  and  $t_P$  into  $v_{IFB}$ 's rate of change incur rising & falling offsets  $v_{IOS}$  and  $v_{IOS}$ . This deviates  $v_{IFB}$ 's peak & valley from  $v_{T(HI)}$  &  $v_{T(LO)}$ , as (1) shows.

$$v_{IOS}^{\pm} = t_{p}^{\pm} \left( \frac{dv_{IFB}}{dt_{E/D}} \right) = t_{p}^{\pm} \left( \frac{di_{L}}{dt_{E/D}} \right) \beta_{IFB} = t_{p}^{\pm} \left( \frac{v_{E/D}}{L_{x}} \right) \beta_{IFB}, \quad (1)$$

where  $v_{E/D}$  is the energize/drain voltage of  $L_X$ .

Since  $t_P^+$  and  $t_P^-$  offsets  $i_L$  and  $v_{IFB}$  in opposite directions, half of the difference between  $v_{IOS}^+$  &  $v_{IOS}^-$  deviates  $v_{IFB(AVG)}$  from  $v_{IR}$  as Fig. 4 shows, which consequently, dictates  $v_{IOS}$ :

$$v_{IOS} = v_{IFB(AVG)} - v_{IR} = \frac{v_{IOS}^{+} - v_{IOS}^{-}}{2} \approx t_{P} \left(\frac{v_{E} - v_{D}}{2L_{X}}\right) \beta_{IFB},$$

(2)

where  $t_P$  is the propagation delay assuming  $t_P^+$  equals  $t_P^-$ , and  $v_E$  and  $v_D$  are  $L_X$ 's energize and drain voltages, respectively.

Oscillation Period:  $t_P$  alters  $\Delta v_{IFB}$  and thus alters oscillation period  $t_{OSC}$ . Since  $v_{IOS}^+$  &  $v_{IOS}^-$  stretches  $\Delta v_{HYS}$  in opposite directions,  $\Delta v_{IFB}$  is  $(v_{IOS}^+ + v_{IOS}^-)$  larger than  $\Delta v_{HYS}$ , as in (3):

$$\Delta v_{IFB} = v_{IFB(HI)} - v_{IFB(LO)} = (v_{T(HI)} + v_{IOS}^{+}) - (v_{T(LO)} - v_{IOS}^{-})$$

$$= \Delta v_{HYS} + v_{IOS}^{+} + v_{IOS}^{-} \approx \Delta v_{HYS} + t_{P} \left(\frac{v_{E} + v_{D}}{L_{X}}\right) \beta_{IFB}$$

(3)

Since  $t_E$  is an energize duty-cycle  $d_E$  fraction of  $t_{OSC}$ , so  $t_{OSC}$  is a reverse  $d_E$  translation of  $t_E$ .  $t_E$ , as Fig. 4 shows, is the time  $v_{IFB}$  takes to slew up across  $\Delta v_{IFB}$ , whose slew rate is  $i_L$ 's slew rate times  $\beta_{IFB}$ . The  $d_E$  of an SL can be found in [3], so  $t_{OSC}$  is:

$$t_{OSC} = \frac{t_{E}}{d_{E}} = \left(\frac{\Delta v_{IFB}}{dv_{IFB}/dt_{E}}\right) \frac{1}{d_{E}} = \left[\frac{\Delta v_{IFB}}{\beta_{IFB}(di_{L}/dt_{E})}\right] \frac{1}{d_{E}}$$

$$= \left(\frac{\Delta v_{IFB}}{\beta_{IFB}}\right) \left(\frac{L_{X}}{v_{E}}\right) \left(\frac{v_{E} + v_{D}}{v_{D}}\right) = \left(\frac{\Delta v_{IFB}}{\beta_{IFB}}\right) \left(\frac{L_{X}}{v_{E} \parallel v_{D}}\right)$$

(4)

. The notation  $v_E \parallel v_D$  shows that  $v_E$  and  $v_D$  combine like parallel impedances. As a result,  $v_E$ 's and  $v_D$ 's combined voltage is lower than the smaller one between  $v_E$  and  $v_D$ .

Fig. 4. Simulated hysteretic oscillation with propagation delay.

## B. Response Time

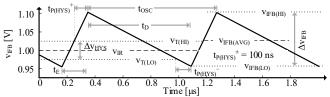

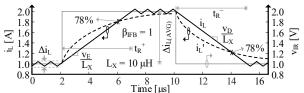

When  $v_{IR}$  changes abruptly as Fig. 5 shows,  $i_{L(AVG)}$  is not able to track  $v_{IR}$  since  $i_L$  cannot change instantaneously. Therefore, the hysteretic relaxation oscillator should be modeled as a transconductor  $A_G$  with delay.

Fig. 5. Simulated hysteretic load dump response.

When  $v_{IR}$  steps up,  $CP_{HYS}$  trips so the SL keeps energizing  $L_X$  and  $i_L$  slews up until  $v_{IFB}$  rises to the new  $v_{IR}$ . The time it takes for  $i_L$  to slew up/down across  $\Delta i_{L(AVG)} = \Delta v_{IR}/\beta_{IFB}$  sets the rising/falling response time  $t_R^+$  and  $t_R^-$  in Fig. 5.  $t_R^\pm$  is:

$$t_{R}^{\pm} = \frac{\Delta i_{L(AVG)}}{di_{L}/dt_{E/D}} = \Delta i_{L(AVG)} \left(\frac{L_{X}}{v_{E/D}}\right) = \left(\frac{\Delta v_{IR}}{\beta_{IFB}}\right) \left(\frac{L_{X}}{v_{E/D}}\right).$$

(5)

Exponential model  $i_L$ ' (dashed line in Fig. 5) approximates the delay of  $i_L$  from  $v_{IR}$ . So based on the approximated  $i_L$ ', a hysteretic pole  $p_{HYS}$  with a time constant  $\tau_{HYS}$  models the actual  $t_R^{\pm}$  in  $A_G$ 's frequency response as (6) shows:

$$A_{G} = \frac{i_{L(AVG)}}{v_{IR}} = \frac{A_{G0}}{1 + s/2\pi p_{HYS}} = \frac{1/\beta_{IFB}}{1 + s\tau_{HYS}}.$$

(6)

$\tau_{HYS}$  is chosen to set  $i_L$ ' to cross  $i_L$  when  $i_L$  reaches 78% of its target as Fig. 5 shows. Thus, positive and negative errors between  $i_L$ ' and  $i_L$  match. (7) & (8) calculate  $\tau_{HYS}$ .  $\tau_{HYS}^{\pm}$  are the  $\tau_{HYS}$  of rising/falling transition, which, may not be equal:

$$78\%\Delta i_{L(AVG)} = \Delta i_{L(AVG)} \left( 1 - \exp \frac{-78\% t_{R}^{\pm}}{\tau_{uvc}^{\pm}} \right), \tag{7}$$

$$\tau_{\text{HYS}}^{\pm} = \frac{78\% t_{\text{R}}^{\pm}}{\ln(1-78\%)} = \frac{t_{\text{R}}^{\pm}}{1.9} = 52\% t_{\text{R}}^{\pm}.$$

(8)

Consequently, the  $p_{HYS}$  that produces the response  $\tau_{HYS}$  sets is:

$$p_{HYS}^{\pm} = \frac{1}{2\pi \tau_{HYS}^{\pm}} \approx \frac{1}{2\pi} \left(\frac{1.9}{t_{R}^{\pm}}\right) = \frac{1.9}{2\pi} \left(\frac{\beta_{IFB}}{\Delta v_{IR}}\right) \left(\frac{v_{E/D}}{L_{X}}\right), \tag{9}$$

where  $p_{HYS}^{\pm}$  are the  $p_{HYS}$  of rising/falling transition, which also, may not be equal.

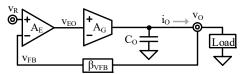

## C. Voltage Loop

Hysteretic current loop (modeled by the  $A_G$ ) is embedded in the voltage loop formed by error amplifier  $A_E$  and voltage feedback  $\beta_{VFB}$  as Fig. 6 shows.  $A_E$  sets error voltage  $v_{EO}$ .  $v_{EO}$  serves the same function as  $v_{IR}$  in Fig. 2, which sets  $i_{L(AVG)}$  & the average output current  $i_{O(AVG)}$ , so that  $v_{FB}$  nears  $v_R$  and  $v_O$  nears  $v_R/\beta_{VFB}$ .

Fig. 6. Hysteretic voltage loop.

Tracing the signal flow around the voltage loop, loop gain A<sub>LG</sub> is:

$$\begin{split} A_{LG} = & \left( \frac{v_{fb}}{v_{o}} \right) \left( \frac{v_{eo}}{v_{fb}} \right) \left( \frac{i_{l(avg)}}{v_{eo}} \right) \left( \frac{i_{o(avg)}}{i_{l(avg)}} \right) \left( \frac{v_{o}}{i_{o(avg)}} \right) = \beta_{VFB} A_{E} A_{G} D_{O} Z_{O} \\ = & \beta_{VFB} \left( \frac{A_{E0}}{1 + s/2\pi p_{AE}} \right) \left( \frac{1/\beta_{IFB}}{1 + s/2\pi p_{HYS}} \right) D_{O} \left( R_{O} \| C_{O} \right) \end{split} , (10) \end{split}$$

where  $A_{E0}$  and  $p_{AE}$  are  $A_E$ 's dc gain and pole,  $D_O$  is the duty-cycle when  $L_X$  is connected to output [3],  $R_O$  is load resistance and  $C_O$  is SL's output capacitor. DC loop gain  $A_{LG0}$  is:

$$A_{LGO} = \beta_{VFB} A_{EO} \left( \frac{1}{\beta_{IFB}} \right) D_O R_O.$$

(11)

Because the  $L_X$ - $C_O$  double pole disappears, output pole  $p_C$  becomes the dominant pole, and unity gain frequency  $f_{OdB}$  is:

$$f_{0dB} \approx A_{LG0} p_C = \frac{A_{LG0}}{2\pi R_0 C_0}$$

(12)

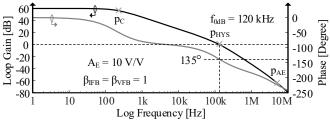

Placing secondary pole  $p_{HYS}$  at  $f_{0dB}$  stabilizes the feedback with 45° phase margin. Fig. 7 shows an example with  $R_O = 100 \Omega$ ,  $C_O = 8.2 \mu F$ , & a load dump  $\Delta i_O = 500$  mA within 1 ns.

Fig. 7. Calculated voltage loop gain.

Finite  $A_E$  offsets  $v_{FB}$  from  $v_R$  by offset  $v_{VOS}$ . So,  $v_{VOS}$  is a reverse  $A_E$  translation from  $v_{EO}$ , as Fig. 6 indicates. Also, non-zero  $v_{IOS}$  offsets  $v_{IFB(AVG)}$  from  $v_{EO}$ , so  $v_{EO}$  is a  $v_{IOS}$  less than  $v_{IFB(AVG)}$ .  $v_{IFB(AVG)}$  carries information about  $i_{L(AVG)}$ , which loads the SL and creates load regulation. Therefore,  $v_{IFB(AVG)}$  is also called loading effect  $v_{LD}$  in this paper, as (13) shows:

$$v_{IFB(AVG)} = i_{L(AVG)} \beta_{IFB} = v_{LD}.$$

(13)

Consequently, v<sub>VOS</sub> is:

$$v_{VOS} = \frac{v_{EO}}{A_E} = \frac{v_{LD} - v_{IOS}}{A_E} = \left[ i_{L(AVG)} - t_p \left( \frac{v_E - v_D}{2L_X} \right) \right] \left( \frac{\beta_{IFB}}{A_E} \right). \quad (14)$$

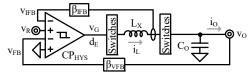

#### D. Contraction

<u>Contracted Loop</u>: Fast  $A_E$  adds significant  $P_Q$  [24–25] & degrades light-load efficiency.  $A_E$  feeds an amplified version of  $v_R - v_{FB}$  to  $CP_{HYS}$ . So, feeding  $v_R$  and  $v_{FB}$  directly to  $CP_{HYS}$  to form a contracted loop as Fig. 8 shows is the same as setting  $A_E$  to 1 since there is no amplification. Since  $A_E$  is the only change, this means previous theory still applies.

The benefit of contraction is less  $P_Q$  since there is one less amplifier. The drawback is worse load regulation since  $A_E$ , which equals one, no longer suppresses  $v_{IOS}$  and  $v_{LD}$ .

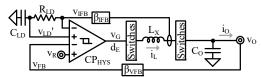

Fig. 8. Contracted hysteretic current-mode voltage loop.

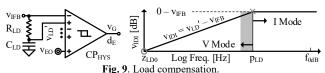

<u>Load Compensation</u>: Canceling the effect of  $v_{LD}$  in the voltage loop compensates load regulation of a contracted loop.  $R_{LD}$  &  $C_{LD}$  in Fig. 9 average  $v_{IFB}$  to  $v_{LD}$ , so  $v_{LD}$  mimics  $v_{LD}$ . So, feeding  $v_{LD}$  and  $v_{IFB}$  to the loop with opposite polarity subtracts  $v_{LD}$  from  $v_{IFB}$ , which effectively cancels the effect of  $v_{LD}$ .

For load-compensated hysteretic power supplies,  $v_{EO}$  sets  $i_{L(AVG)}$ . Only the  $\Delta i_L$  information is enough to let  $CP_{HYS}$  sustain oscillation such that  $i_L$  behaves like  $A_G$ .  $v_{LD'} - v_{IFB}$ , which is called the differential current mode voltage  $v_{IDI}$  in this paper, is 0 at dc and rises as frequency rises. Its amplitude flattens out past load-compensation pole  $p_{LD}$  as Fig. 9 shows.  $v_{IDI}$  only feeds high-frequency  $\Delta i_L$  information to  $CP_{HYS}$ , which sustains oscillation, so the  $i_L$  behaves like  $A_G$  passed  $p_{LD}$ .  $p_{LD}$  is:

$$p_{LD} = \frac{1}{2\pi R_{LD} C_{LD}} << f_{0dB}.$$

(15)

To stabilize the voltage loop,  $i_L$  must behave like a transconductor before reaching  $f_{0dB}$ . This guarantees that  $p_{LC}$  never surfaces, & the voltage loop reaches  $f_{0dB}$  with one pole. So,  $p_{LD}$  must be much less than  $f_{0dB}$ . Fig. 10 shows a load compensated contracted loop. Since  $v_{LD}$ 's effect is removed,  $v_{VOS}$  equals  $v_{IOS}$ .

Fig. 10. Load-compensated contracted hysteretic loop.

## III. COMPACT LI-ION 5-V DESIGN

#### A. IoT Wireless Microsensors

IoT sensors demand 4.5–5.5 V supply voltage  $v_0$  [26–27]. Li-Ion batteries provide SL supplies with 2.7–4.2 V input voltage  $v_{\rm IN}$  [28]. The duration  $t_{\rm XFER}$  of sensor transfer events is 7–360 ms [6, 29]. IoT sensors can source up to 480 mA from the supply (LL-RXR-27 Transceiver). Maximum response time  $t_{\rm R(MAX)}$  is set to 0.1% of  $t_{\rm XFER(MIN)}$ . Table I lists constraints.

TABLE I: DESIGN CONSTRAINTS

| Parameter              | Value | Parameter              | Value  | Parameter           | Value  |

|------------------------|-------|------------------------|--------|---------------------|--------|

| V <sub>IN(MIN)</sub>   | 2.7 V | V <sub>IN(MAX)</sub>   | 4.2 V  | $v_R$               | 1.2 V  |

| V <sub>O(MIN)</sub>    | 4.5 V | $v_{O}$                | 5.0 V  | V <sub>O(MAX)</sub> | 5.5 V  |

| t <sub>XFER(MIN)</sub> | 7 ms  | t <sub>XFER(MAX)</sub> | 360 ms | $t_{R(MAX)}$        | *7 µs  |

| $\Delta v_{HYS}$       | 50 mV | ${t_P}^\pm$            | 20 ns  | i <sub>O(MAX)</sub> | 480 mA |

\*Targeting  $t_{R(MAX)} = 0.1\%t_{XFER(MIN)}$ .

## B. Power Stage

<u>Transfer Inductor</u>: The power stage must be a boost since  $v_{IN(MAX)}$  is less than  $v_{O(MIN)}$ .  $L_X$  is selected to meet  $t_R$  constraints. Worst-case  $t_R$  occurs with max  $\Delta i_{L(AVG)}$  and

slowest  $i_L$  slew. Since  $i_{L(AVG)}$  is a reverse  $D_O$  translation of  $i_O$ , worst-case  $t_R$  also occurs with  $D_{O(MIN)}$  &  $v_{IN(MIN)}$ , as in (17).

$$t_{R} \leq \frac{\Delta i_{L(AVG,MAX)}}{\left(di_{L}/dt_{E}\right)_{(MIN)}} = \left(\frac{i_{O(MAX)} - 0}{D_{O(MIN)}}\right) \left(\frac{L_{X}}{v_{IN(MIN)}}\right) \leq t_{R(MAX)}. \quad (17)$$

Solving (17) gives  $L_X < 21 \mu H$ . For miniaturization, the design uses a 3.3- $\mu H$  1.0  $\times$  0.6  $\times$  0.6 mm<sup>3</sup>  $L_X$  (Murata LQ Series).

Output Capacitor:  $C_O$  is selected to meet  $v_{O(MIN)}$  constraint. Max load dump  $\Delta i_{O(MAX)}$  occurs when  $i_O$  steps from 0 to  $i_{O(MAX)}$ . With  $t_{R(MAX)}$  and  $\Delta i_{O(MAX)}$ ,  $v_O$  should never drop blow  $v_{O(MIN)}$ . This means  $C_O$ 's voltage drop  $\Delta v_{CO}$  must be less than:

$$\Delta v_{CO} \le \left(\frac{i_{O(MAX)} - 0}{C_O}\right) t_{R(MAX)} \le v_O - v_{O(MIN)}. \tag{18}$$

Solving (18) gives  $C_O > 6.7 \mu F$ . For design margin, this work uses a 10- $\mu F$   $1.0 \times 0.5 \times 0.5 \text{ mm}^3$   $C_O$  (Samsung CL05 Series).

## C. Control Design

<u>Frequency Response</u>: in addition to pc, p<sub>HYS</sub>, p<sub>AE</sub>, p<sub>LD</sub>, and  $z_{LD0}$ , SL boost carries right-half-plane (RHP) zero  $z_{RHP}$  at [9]:

$$z_{RHP} = \frac{V_{o}D_{o}}{2\pi L_{x}i_{L(HI)}} = \frac{V_{o}D_{o}}{2\pi L_{x}(i_{L(AVG)} + 0.5\Delta i_{L})}.$$

(19)

Duty-cycled output is the cause of  $z_{RHP}$  [30, 32].  $z_{RHP}$  loses 90° phase, which makes stabilizing the voltage loop challenging.

<u>Stability</u>:  $D_{O(MIN)}$  and highest  $i_{L(AVG)}$  result in lowest RHP zero  $z_{RHP(MIN)}$ . Calculated  $z_{RHP(MIN)}$  is 140 kHz. Worst-case  $t_R$  results in lowest hysteretic pole  $p_{HYS(MIN)}$  & calculated  $p_{HYS(MIN)}$  is 280 kHz. Placing the lower one of  $z_{RHP(MIN)}$  and  $p_{HYS(MIN)}$  above  $f_{0dB}$  stabilizes the loop with more than 45° phase margin:

$$f_{0dB} = \frac{\beta_{VFB} A_{E0} D_{O}}{2\pi C_{O} \beta_{EFB}} \le \min \{ p_{HYS(MIN)}, z_{RHP(MIN)} \}$$

(20)

Assuming an ideal  $\beta_{VFB} \approx v_R/v_O = 24\%$ , setting  $A_{E0} = 50 \text{ V/V}$  as a design choice and choosing  $\beta_{IFB} = 1 \Omega$  satisfies (20).

Offset Correction: Fine-tuning  $\beta_{VFB}$  centers  $v_O$  around its target:  $v_R/\beta_{VFB}$ . Targeting mid-way  $i_O = 0.5i_{O(MAX)}$ , calculated  $v_{VOS}$  is 8.9 mV and calculated  $\beta_{VFB}$  is 23.8% as (21) shows.

$$\beta_{\text{VFB}} = \frac{v_{\text{FB}}}{v_{\text{O}}} = \frac{v_{\text{R}} - v_{\text{VOS}}}{v_{\text{O}}}.$$

(21)

# IV. VALIDATION

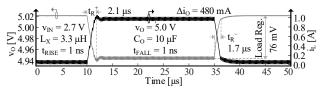

# A. Load Dump Response

Simulated  $i_L$  &  $v_O$  under  $\pm$  480-mA 1-ns load dumps are shown in Fig. 11.  $t_R^+$  &  $t_R^-$  are 2.1  $\mu$ s & 1.7  $\mu$ s.  $v_O$  never droops below the 4.5-V  $v_{O(MIN)}$ , so this design meets the target Table I sets. However,  $v_O$  deviates statically by 76 mV across 480-mA load change  $\Delta i_O$ . This translates to 160 mV/A load regulation, which is to be reduced in the next sub-section.

Fig. 11. Simulated load dump transient of designed hysteretic boost.

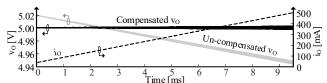

#### B. Load Regulation

Load compensator  $R_{LD}=4~M\Omega$  and  $C_{LD}=4~pF$  places  $p_{LD}$  at 10 kHz, which is much lower than the calculated  $f_{0dB}$  (102 kHz) as (15) requires. To simulate load regulation,  $i_{O}$  rises very slowly from 50 to 500 mA across 9.5 ms as the dash line in Fig. 12 shows. Simulated  $v_{O}$  with & without compensation are shown as solid black and grey in Fig. 12. Without compensation,  $v_{O}$  drops from 5.02 V to 4.94 V, which agrees with Fig. 11. With compensation,  $v_{O}$ 's average hardly drops.

Fig. 12. Simulated load regulation with & without compensation.

$v_{O}$ 's ripple  $\Delta v_{O(AC)}$  rises from 0.7 mV to 5.4 mV as  $i_{O}$  rises. With a  $\Delta i_{O}$  of 480 mA,  $v_{O}$ 's error  $\Delta v_{O(LD)}$  is about 80 mV. Table II lists performances of the designed hysteretic supply.

TABLE II: PERFORMANCE

| Name                        | Value      | Name               | Value  | Name     | Value   | Name                    | Value  |

|-----------------------------|------------|--------------------|--------|----------|---------|-------------------------|--------|

| $v_{IN}$                    | 2.7 V      | $v_{O}$            | 5.0 V  | $t_{SW}$ | 4.7 MHz | $\Delta i_{\mathrm{O}}$ | 480 mA |

| $\Delta v_{O(AC)}$          | 0.7-5.4 mV | $\Delta v_{O(LD)}$ | 80 mV  | $L_{X}$  | 3.3 μΗ  | Co                      | 10 μF  |

| t <sub>p</sub> <sup>+</sup> | 2.1 us     | t₀-                | 1.7 us | 10(MAY)  | 500 mA  | _                       | _      |

## C. SoA Comparison

This analysis is applicable to a generic power stage given its frequency response (which can be found in [30]), unlike analyses in [20–21] that are only applied to SL bucks. This analysis is also applicable to different control schemes, like contracted and load-compensated loops.

This analysis includes IC design issues, such as  $t_P$ ,  $v_{VOS}$ ,  $v_{IOS}$ , and the resulting load regulation. Since analyses in [12–21] assume ideal control loops, so only the proposed analysis provides more complete insights & guidance on designing IC-level hysteretic SL power supplies.

Valuable analyses in [12–19] are based strictly on non-linear control theory, which make them very solid & thorough. In addition to the SoA, the proposed analysis hinges on insights and provides straight-forward expressions on  $L_X$ ,  $C_O$ ,  $A_{EO}$ ,  $\beta_{VFB}$ ,  $\beta_{IFB}$ ,  $R_{LD}$ , and  $C_{LD}$  that set IC designers ready for practical chip-level implementations.

# V. CONCLUSIONS

This paper presents an insightful IC-design oriented analysis on hysteretic current-mode switched-inductor (SL) power supplies. The fundamental attribute of this analysis is realizing that a hysteretic loop is fundamentally a relaxation oscillator and should be modeled using a transconductor with one pole. The proposed analysis applies to a generic SL power stage and incorporates practical IC design concerns that are mostly absent in prior analyses (i.e., propagation delay, current and voltage offset, contraction, and load compensation). With straight-forward expressions, this analysis guides the design on inductor and capacitor selection, error amplifier gain, voltage and current feedback factors, and load compensators, and prepares IC designers with a ready-to-use workflow.

#### REFERENCES

- [1] L. D. Xu, W. He and S. Li, "Internet of things in industries: a survey," in *IEEE Transactions on Industrial Informatics*, vol. 10, no. 4, pp. 2233-2243. Nov. 2014.

- [2] T. Torfs, et al., "Low power wireless sensor network for building monitoring," in *IEEE Sensors Journal*, vol. 13, no. 3, pp. 909-915, 2013.

- [3] D. Sehrawat and N. S. Gill, "Smart sensors: analysis of different types of IoT sensors," 2019 3rd International Conference on Trends in Electronics and Informatics (ICOEI), 2019, pp. 523-528.

- [4] S. Sarkar and S. Misra, "From micro to nano: the evolution of wireless sensor-based health care," in *IEEE Pulse*, vol. 7, no. 1, pp. 21-25, 2016.

- [5] S. Liu et al., "Handheld photoacoustic imager for theranostics in 3D," in IEEE Transactions on Medical Imaging, vol. 38, no. 9, pp. 2037-2046, Sept. 2019.

- [6] M. Flatscher et al., "A bulk acoustic wave (BAW) based transceiver for an in-tire-pressure monitoring sensor node," in *IEEE Journal of Solid-State Circuits*, vol. 45, no. 1, pp. 167-177, Jan. 2010.

- [7] T. Chang and G. A. Rincón-Mora, "Lowest V<sub>IN</sub> possible for switched-inductor boost converters," *IEEE 62nd International Midwest Symposium on Circuits and Systems (MWSCAS)*, 2019, pp. 798-801.

- [8] A. A. Blanco and G. A. Rincón-Mora, "Compact fast-waking light/heat-harvesting 0.18-µm CMOS switched-inductor charger," in *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 65, no. 6, pp. 2024-2034, June 2018.

- [9] G. A. Rincón-Mora, "Power IC Design: Top-Down Approach", Lulu Press Inc., Morrisville, North Carolina, 2016.

- [10] A. Paidimarri and A. P. Chandrakasan, "A wide dynamic range buck converter with sub-nW quiescent power," in *IEEE Journal of Solid-State Circuits*, vol. 52, no. 12, pp. 3119-3131, Dec. 2017.

- [11] W. Fu, S. T. Tan, M. Radhakrishnan, R. Byrd and A. A. Fayed, "A DCM-only buck regulator with hysteretic-assisted adaptive minimumon-time control for low-power microcontrollers," in *IEEE Transactions* on *Power Electronics*, vol. 31, no. 1, pp. 418-429, Jan. 2016.

- [12] P. Mattavelli, L. Rossetto and G. Spiazzi, "Small-signal analysis of dedc converters with sliding mode control," in *IEEE Transactions on Power Electronics*, vol. 12, no. 1, pp. 96-102, Jan. 1997.

- [13] Yan-Fei Liu and P. C. Sen, "Large-signal modeling of hysteretic currentprogrammed converters," in *IEEE Transactions on Power Electronics*, vol. 11, no. 3, pp. 423-430, May 1996.

- [14] S. Tan, Y. M. Lai and C. K. Tse, "General design issues of sliding-mode controllers in dc-dc converters," in *IEEE Transactions on Industrial Electronics*, vol. 55, no. 3, pp. 1160-1174, March 2008.

- [15] S. K. Mishra and K. D. T. Ngo, "Dynamic characterization of the synthetic ripple modulator in a tightly regulated distributed power application," in *IEEE Transactions on Industrial Electronics*, vol. 56, no. 4, pp. 1164-1173, Apr. 2009.

- [16] Jian Sun, "Small-signal modeling of variable-frequency pulsewidth modulators," in *IEEE Transactions on Aerospace and Electronic Systems*, vol. 38, no. 3, pp. 1104-1108, July 2002.

- [17] J. h. Park and B. H. Cho, "Small signal modeling of hysteretic current mode control using the PWM switch model," *IEEE Workshops on Computers in Power Electronics*, 2006, pp. 225-230.

- [18] K. Lee, F. C. Lee and M. Xu, "A hysteretic control method for multiphase voltage regulator," in *IEEE Transactions on Power Electronics*, vol. 24, no. 12, pp. 2726-2734, Dec. 2009.

- [19] R. Redl, "Small-signal high-frequency analysis of the free-running current-mode-controlled converter," *IEEE Power Electronics Specialists Conference*, 1991, pp. 897-906.

- [20] T. Nabeshima, T. Sato, S. Yoshida, S. Chiba and K. Onda, "Analysis and design considerations of a buck converter with a hysteretic PWM controller," 2004 IEEE 35th Annual Power Electronics Specialists Conference, vol. 2, pp. 1711-1716, 2004.

- [21] C. C. Chuang, H. P. Chou and M. L. Chiu, "A buck converter using accurate synthetic ripple hysteresis control scheme," *IEEE Ninth International Conference on Power Electronics and Drive Systems*, 2011, pp. 682-686.

- [22] I. E. Getreu, A. D. Hadiwidjaja and J. M. Brinch, "An integrated-circuit comparator macromodel," in *IEEE Journal of Solid-State Circuits*, vol. 11, no. 6, pp. 826-833, Dec. 1976.

- [23] H. A. Mantooth and P. E. Allen, "A behavioral model of an analog voltage comparator," *Proceedings of the 32nd Midwest Symposium on Circuits and Systems*, pp. 989-992 vol.2, pp. 989-992, 1989.

- [24] J. Suh, J. Seok and B. Kong, "A fast response PWM buck converter with active ramp tracking control in a load transient period," in *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 66, no. 3, pp. 467-471, March 2019.

- [25] Jeongjin Roh, "High-performance error amplifier for fast transient DC-DC converters," in *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 52, no. 9, pp. 591-595, Sept. 2005.

- [26] SG Wireless, SGW8100 + 30 dBm LoRa Modem.

- [27] B. Martinez, M. Montón, I. Vilajosana and J. D. Prades, "The power of models: modeling power consumption for IoT devices," in *IEEE Sensors Journal*, vol. 15, no. 10, pp. 5777-5789, Oct. 2015.

- [28] Lijun Gao, Shengyi Liu and R. A. Dougal, "Dynamic lithium-ion battery model for system simulation," in *IEEE Transactions on Components* and Packaging Technologies, vol. 25, no. 3, pp. 495-505, Sept. 2002.

- [29] T-Mobile, "NB-IoT, LoRaWAN, Sigfox: An up-to-date comparison," Deutsche Telekom AG, Germany, Apr. 2021.

- [30] R. Erickson, "Fundamentals of Power Electronics," Springer, 2020.

- [31] G. A. Rincón-Mora, "Analog Electronics: Filters, Amps, & Oscillators," New York: KDP, 2019.

- [32] G. W. Wester and R. D. Middlebrook, "Low-frequency characterization of switched dc-dc converters," in *IEEE Transactions on Aerospace and Electronic Systems*, vol. AES-9, no. 3, pp. 376-385, May 1973.