# Maximum DC–DC Conversion in Switched-Inductor Power Supplies

Qiwei Chen, Graduate Student Member, IEEE, and Gabriel A. Rincón-Mora, Fellow, IEEE School of Electrical and Computer Engineering, Georgia Institute of Technology, Atlanta, GA, U.S.A.

aren\_chen@gatech.edu and rincon-mora@gatech.edu

Abstract—High DC-DC voltage conversion is crucial in many emerging fields. However, the maximum achievable voltage conversion of switched-inductor power supplies (SLPS) has been a lingering question. This paper first establishes the inversely proportional relationship between minimum duty cycle and maximum conversion ratio in ideal SLPS. Then, how propagation delays limit the minimum duty cycle is found. The difference between actual and ideal duty cycle, caused by losses in the power stage, is analyzed. By translating delay-limited minimum duty cycle and loss-induced duty cycle shift into ideal SLPS's duty cycle, the maximum conversion of any actual SLPS can be determined. The paper also discusses the dominant loss for duty cycle shift at different operating conditions and the loading effect of losses. For validation, a buck and a boost example are simulated with SPICE. In summary, this paper presents expressions and insights to analyze and understand maximum DC-DC conversion of SLPS.

Keywords—Propagation delay, power losses, maximum voltage gain, voltage translation, buck-boost, extreme duty ratio.

#### I. DC-DC CONVERSION IN POWER-SUPPLY SYSTEMS

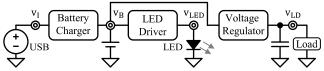

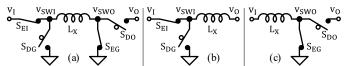

Power supplies are essential for all systems that require external electrical power to operate. DC–DC power supplies are designed to sustain a constant voltage or current from a constant input voltage, examples of which are shown in Fig. 1.

Fig. 1. Types of power DC–DC power supplies.

Many emerging fields, such as USB power delivery, electric vehicle, and computation center, require power supplies to step-up or step-down voltages by high ratios. Most literatures on high DC–DC conversion power supplies utilized cascaded power stages, such as multiple switched-inductors [1]–[3], or switched-inductor/capacitor hybrid [4]–[12]. They all need additional components and usually more complex control schemes compared to standalone switched-inductor power supplies (SLPS) [13]–[19]. However, these costs for high DC–DC conversion applications remain unjustified unless the conversion exceeds the capability of SLPS. Past discussions have touched upon some factors' impact on voltage conversion of certain SLPS [4], [20]–[24]. But the general conversion limit of SLPS is largely unexplored in the state-of-the-art.

In this paper, theory to find maximum DC-DC conversion ratio of SLPS is developed and validated with simulation. Section II introduces the operation and maximum conversion ratio of ideal SLPS, while Section III and IV explain how propagation delay and power losses impose limitation on real

This work is supported by Analog Devices.

systems. Section V reveals the approach to find realistic maximum DC–DC conversion ratio and provides simulation validation of the theory, and Section VI concludes the paper.

# II. SWITCHED-INDUCTOR DC-DC CONVERSION

### A. Operation

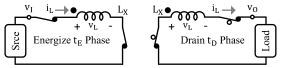

In SLPS, the switched-inductor  $L_X$  serves as an energy storage device that receives and delivers energy in alternating energize and drain phases, as shown in Fig. 2. Across energize time  $t_E$ , inductor voltage  $v_L$  includes input voltage  $v_I$ , and in drain time  $t_D$ , it includes output voltage  $v_O$  to supply the load from source.

Fig. 2. Phases of switched-inductor.

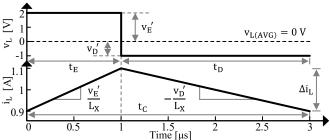

As Fig. 3 shows, in steady state, across conduction time  $t_C$ ,  $v_L$  switches between ideal energize voltage  $v_E{}'$  during  $t_E$  and ideal drain voltage  $v_D{}'$  during  $t_D$ , keeping an average  $v_L$  of 0 V. Meanwhile, inductor current  $i_L$  rises and falls by the same ripple current  $\Delta i_L$  that can be calculated with:

$$\Delta i_{L} = t_{E} \left( \frac{di_{L}}{dt_{E}} \right) = t_{E} \left( \frac{v_{E}'}{L_{X}} \right) = t_{D} \left( \frac{v_{D}'}{L_{X}} \right). \tag{1}$$

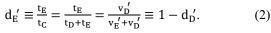

The ideal energize duty cycle  $d_E'$ , the  $t_E$  fraction of  $t_C$ , can also be represented by  $v_E'$  and  $v_D'$ , and it sums to 1 with the ideal drain duty cycle  $d_D'$ :

Fig. 3. Simulated switched-inductor waveforms.

#### B. Conversion Ratio

As (2) shows,  $v_D'$  exceeds  $v_E'$  when  $d_E'$  is above 50 % and *vice versa*. An ideal buck-boost converter, shown in Fig. 4(a), can convert-up or convert-down  $v_E'$  to  $v_D'$ , which are  $v_I$  and  $v_O$ , as shown in Table I. Buck or boost converter in Fig. 4(b) or (c) are variations of buck-boost, with the absence of output or input switches. Their  $v_O$ 's can only be lower or higher than  $v_I$ .

Fig. 4. Ideal (a) buck-boost, (b) buck, and (c) boost converters.

| TABLE I. | IDEAL ' | Voltages <i>a</i> | AND DUTY RATIOS |

|----------|---------|-------------------|-----------------|

|          |         |                   |                 |

|            | $v_E^{\prime}$ | $v_{\scriptscriptstyle D}^{\prime}$ | $d_I'$    | $d_o'$                                |

|------------|----------------|-------------------------------------|-----------|---------------------------------------|

| Buck-Boost | $v_I$          | $v_o$                               | $d_E^{'}$ | $d_{D}^{\ \prime}$                    |

| Buck       | $v_I - v_O$    | $v_0$                               | $d_E^{'}$ | 1                                     |

| Boost      | $v_I$          | $v_0 - v_I$                         | 1         | $d_{\scriptscriptstyle D}^{\;\prime}$ |

The up or downward conversion ratio  $K_{V(\downarrow/\uparrow)}$  from  $v_I$  to  $v_O$  is always larger than 1 V/V. The input and output switching node voltages  $(v_{SWI}$  and  $v_{SWO})$  are duty-cycle fractions of  $v_I$  and  $v_O$ . Since  $v_{L(AVG)}$  is 0 V,  $v_{SWI}$  and  $v_{SWO}$  have the same average value.  $K_{V(\downarrow/\uparrow)}$  is then the ratio between  $d_I'$  and  $d_O'$ , the duty cycles of  $L_X$  connecting to  $v_I$  and  $v_O$  respectively:

$$K_{V(\downarrow/\uparrow)} \equiv \frac{v_{I/O}}{v_{O/I}} = \left(\frac{v_{SWI/O(AVG)}}{d_{I/O}'}\right) \left(\frac{d_{O/I}'}{v_{SWO/I(AVG)}}\right) = \frac{d_{O/I}'}{d_{I/O}'}. \quad (3)$$

# C. Conversion Limit

The maximum conversion ratio  $K_{V(\downarrow/\uparrow)}^{MAX}$  would then be the ratio between maximum and minimum  $d_I'$  or  $d_O'$ . By variable substitution, it can be expressed with only minimum  $d_{E/D}'$ , or  $d_{MIN}'$  in short, for buck–boost (BB), buck (BK), and boost (BS):

$$K_{V(\downarrow\uparrow\uparrow)}^{\text{MAX}} = \frac{d_{\text{O/I(MAX)}}'}{d_{\text{I/O(MIN)}}'} = \underbrace{\underbrace{\frac{1 - d_{\text{E/D(MIN}}'}}{d_{\text{E/D(MIN})}'}}_{K_{V(BB)}^{\text{MAX}}} \approx \underbrace{\frac{1}{d_{\text{E/D(MIN}}'}}_{K_{V(BK/BS)}^{\text{MAX}}} \equiv \frac{1}{d_{\text{MIN}}'}. (4)$$

#### III. DELAY LIMIT

It is now established that  $d_{MIN}'$  is the limiting factor for  $K_{V(\downarrow/\uparrow)}^{MAX}$ . Ideally,  $d_{MIN}'$  can approach 0 % and  $K_{V(\downarrow/\uparrow)}^{MAX}$  can approach  $\infty$ . However, in an actual system, there is a minimum energize or drain duty cycle provided to the switches,  $d_{MIN}$ .

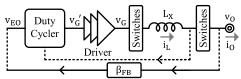

#### A. Control Loop

Fig. 5 shows a simplified control loop diagram of SLPS, where the properties to be controlled, such as  $v_0$  or  $i_0$ , are sensed and fed to the circuits that process the information into a control signal  $v_{E0}$ . The duty cycler then translates  $v_{E0}$  into an alternating duty cycle command  $v_G'$  that the driver uses to turn the switches on and off. In steady state, the feedback signal and  $v_{E0}$  are constant, while the duty cycler and the driver operate switches at  $d_{E/D}$ , with  $d_{MIN}$  possible.

Fig. 5. Typical feedback loop in SL power supplies.

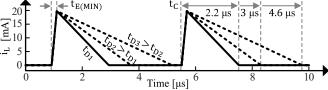

### B. Discontinuous-Conduction Mode

In Discontinuous-Conduction Mode (DCM),  $t_C$  is a fraction of the switching period  $t_{SW}$ . After the drain phase,  $i_L$  remains at 0 until the next  $t_{SW}$  begins. As Fig. 6 shows, even with minimum energize time  $t_{E(MIN)}$ ,  $d_E$  can still decrease with  $t_C$  extending into the zero-current period. The same applies to decreasing  $d_D$ .

So,  $d_{MIN}$  limit is not reached until  $t_C$  approaches  $t_{SW}$ , and the operation is hastened to Continuous-Conduction Mode (CCM).

Fig. 6. Simulated conduction times.

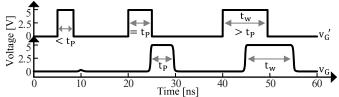

#### C. Continuous-Conduction Mode

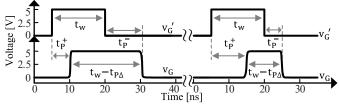

In CCM,  $t_C$  equals  $t_{SW}$ , and  $d_{MIN}$  is dependent on  $t_{SW(MAX)}$  and  $t_{E/D(MIN)}$ . For a component with propagation delay  $t_P$ , it can only reproduce inputs no shorter than  $t_P$ , as Fig. 7 shows.

Fig. 7. Simulated pulse widths.

In order to provide a valid signal at the switches,  $v_{EO}$  should contain information of  $t_{E/D}$  longer than any individual propagation delay  $t_{P(x)}$  between  $v_{EO}$  and the switches. However, the rising and falling propagation delay of a component,  $t_p^+$  and  $t_p^-$ , may vary from each other by:

$$t_{P\Delta} \equiv t_P^+ - t_P^-. \tag{5}$$

Fig. 8 shows waveforms of two drivers that have  $t_{P\Delta}$  of opposite signs. A negative or a positive  $t_{P\Delta}$  extends or shortens the active-high energize signal, subtracting itself from the pulse width. Similarly,  $t_{P\Delta}$  adds itself to an active-low drain pulse.

Fig. 8. Simulated asymmetric delays.

Therefore, the longest  $t_{P(x)}$ , or  $t_{P(MAX)}$ , and the sum of all the subsequent  $t_{P\Delta}$ , or  $t_{P\Sigma\Delta}$ , determine  $t_{E/D(MIN)}$ . So  $d_{MIN}$  is:

$$d_{MIN} = \frac{t_{E/D(MIN)}}{t_{SW(MAX)}} = \frac{Max\{t_{P(x)}\} \mp \Sigma_{j>x} t_{P\Delta(j)}}{t_{SW(MAX)}} \equiv \frac{t_{P(MAX)} \mp t_{P\Sigma\Delta}}{t_{SW(MAX)}}, (6)$$

assuming  $t_{P\Sigma\Delta}$  is subtracted from active-high  $t_E$  and added to active-low  $t_D$ . However, different control methods of SLPS could impose some variations on (6).

*PWM Loop:* In Pulse-Width Modulation (PWM) control, the duty cycler has a fixed  $t_{SW}$ . In this scheme,  $d_{MIN}$  is determined solely by  $t_{E/D(MIN)}$ , or the delays. The expression for  $d_{MIN}$  would be (6) with a constant denominator  $t_{SW}$ .

*Valley/Peak Loop:*  $t_E$  or  $t_D$  can be designed to be constant in valley or peak loop. Such,  $d_{E(MIN)}$  in valley loop and  $d_{D(MIN)}$  in peak loop are limited by  $t_{SW(MAX)}$ , or the lowest switching frequency  $f_{SW}$  allowed before the control loop's response time

and stability is impacted by  $f_{SW}$  approaching the unity gain frequency. In this case, the numerator in (6) should be constant  $t_{E/D}$ . In the alternative case that variable  $t_D$  or  $t_E$  is very short and  $t_{SW}$  is close to the preset  $t_E$  or  $t_D$ , (6) shows approximate expression of  $d_{MIN}$  when the denominator is constant  $t_{E/D}$ .

Hysteretic Loop: The power supplies can also be controlled by limiting  $i_L$  within a window. Since the enegize or drain actions are administered whenever  $i_L$  reaches the boundaries, there is no preset  $t_{E/D}$  or  $t_{SW}$ . Hence, (6) is accurate.

#### IV. POWER-LOSS DUTY CYCLE SHIFT

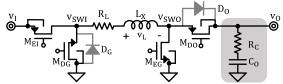

Though  $d_{MIN}$  can be found with delays, (4) cannot be directly applied to a real, lossy system in which  $v_L$  is altered. This section analyzes the effects of power losses on a synchronous buck–boost shown in Fig. 9. Since buck and boost are buck–boost without certain components, their losses are naturally included in this analysis. Output capacitor  $C_0$  and its series resistance  $R_C$  may not always be present in all SLPS.

Fig. 9. Power stage of buck-boost converter.

#### A. Conduction-Path Losses

Across  $t_E$ , current flows in the direction of  $v_E'$ . Losses along the conduction path reduces  $v_E'$  into  $v_E$ , the actual  $v_L$  during  $t_E$ :

$$v_E \approx v_E' - i_{L(AVG)} R_E - v_{IV(E)}, \tag{7}$$

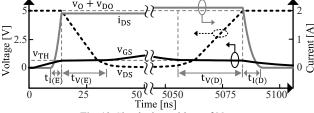

where  $R_E$  is the resistance in energize path and  $v_{IV(E)}$  is the average energize voltage reduced by switches' current-voltage (IV) overlap transient. As left of Fig. 10 shows, when  $v_{GS}$  rises to  $v_{TH}$ ,  $M_{EG}$ 's  $v_{DS}$  falls about linearly as the switch closes. Across interval  $t_{V(E)}$ ,  $v_E$  is reduced by the average voltage  $v_{DS}$  traverses,  $0.5(v_O + v_{DO})$ . Similarly,  $v_{DS}$  of  $M_{EI}$  traversing through  $v_I + v_{DG}$  contribute to a lower  $v_E$ . We can then derive:

$$v_{\rm IV(E/D)} \approx \left(\frac{t_{\rm V,EI(E/D)}}{t_{\rm E/D}}\right) \left(\frac{v_{\rm I} + v_{\rm DG}}{2}\right) + \left(\frac{t_{\rm V,EG(E/D)}}{t_{\rm E/D}}\right) \left(\frac{v_{\rm O} + v_{\rm DO}}{2}\right),~(8)$$

where  $v_{DG}$  and  $v_{DO}$  are diode voltages of  $D_G$  and  $D_O$ , which can have different values for Silicon, Schottky, or MOS diode. The IV overlap effects of  $M_{DG}$  and  $M_{DO}$  are negligible as their  $v_{DS}$ 's traverse only  $v_{DG}$  and  $v_{DO}$  across short  $t_V$ 's.

Fig. 10. Simulted transitions of M<sub>EG</sub>.

Across  $t_D$ , current flows in the reverse direction of  $v_D'$ . The effects of drain path resistance  $R_D$ , additional diode voltages during dead time  $t_{DT}$ , and IV overlap transients raises  $v_D'$  to  $v_D$ :

$$v_D \approx v_D' + i_{L(AVG)}R_D + v_{DT(D)} - v_{IV(D)}.$$

(9)

$v_{DT(D)}$  in (10) shows the average effect of diode drops on  $v_D$  during  $t_{DT}$ . In the case of an asynchronous system,  $R_D$  contains no resistance of  $M_{DG}$  and  $M_{DO}$ , and  $2t_{DT}$  equals  $t_D$  in:

$$v_{\rm DT(D/SW)} = \left(\frac{2t_{\rm DT}}{t_{\rm D/SW}}\right) (v_{\rm DG} + v_{\rm DO}).$$

(10)

As right of Fig. 10 shows, after  $M_{EG}$ 's  $v_{GS}$  drops to  $v_{TH}$ ,  $v_{DS}$  does not rise instantaneously but linearly across  $t_{V(D)}$ , reducing  $v_D$ . This effect of  $M_{EG}$  and  $M_{EI}$ 's IV overlap is  $v_{IV(D)}$  in (8).

# B. Energize Duty-Cycle Shift

The energize duty cycle in a lossy system can then be expressed in terms of the actual  $v_E$  and  $v_D$  applied on  $L_X$ :

$$d_{E} = \frac{v_{D}}{v_{E} + v_{D}} \approx \frac{v_{D}' + i_{L(AVG)} R_{D} + v_{DT(D)} - v_{IV(D)}}{v_{E}' + v_{D}' + i_{L(AVG)} (R_{D} - R_{E}) + v_{DT(D)} - v_{IV(D)} - v_{IV(E)}}, (11)$$

and the shift in energize duty cycle between lossy and lossless system, under identical  $v_E'$  and  $v_D'$ , would be:

$$\Delta d_{E} = d_{E} - d_{E}' = \frac{i_{L(AVG)}R_{EQ} + v_{DT(SW)} + v_{IV(SW)}}{v_{F}' + v_{D}'}, \quad (12)$$

where  $R_{EQ}$  is the weighted average of  $R_E$  and  $R_D$  based on their respective duty cycles, and is approximately the sum of  $R_L$ , MOSFET resistance in a conduction path  $R_M$ , and a fraction of  $R_C$  that conducts  $(1 - d_O)$  inductor current for  $d_O$  period:

$$R_{EO} = d_E R_E + (1 - d_E) R_D \approx R_L + R_M + d_O (1 - d_O) R_C.$$

(13)

The effect of dead time across  $t_{SW}$  would be  $v_{DT(SW)}$  shown in (11), and IV overlap's combined effect simplifies to:

$$\mathbf{v}_{\mathrm{IV}(\mathrm{SW})} = \left(\frac{\mathbf{t}_{\mathrm{V}\Delta,\mathrm{EI}}}{\mathbf{t}_{\mathrm{SW}}}\right) \left(\frac{\mathbf{v}_{\mathrm{I}} + \mathbf{v}_{\mathrm{DG}}}{2}\right) + \left(\frac{\mathbf{t}_{\mathrm{V}\Delta,\mathrm{EG}}}{\mathbf{t}_{\mathrm{SW}}}\right) \left(\frac{\mathbf{v}_{\mathrm{O}} + \mathbf{v}_{\mathrm{DO}}}{2}\right), \quad (14)$$

where  $t_{V\Delta,EI/EG}$  is  $t_{V,EI/EG(E)} - t_{V,EI/EG(D)}$ . As combined effect of all three components,  $\Delta d_E$  represents the amount by which  $d_E$  must increase in a lossy power stage compared to an ideal power stage energized and drained by the same  $v_I$  and  $v_O$ .

Inspecting (12), we find that only the  $R_{EQ}$  factor increases linear with  $i_{L(AVG)}$ , inferring that resistance is the dominant  $\Delta d_E$  contributor in high-current systems. However, the insignificant, natural-logarithmically increasing (respect to  $i_{L(AVG)})\,v_{DT(SW)},$  becomes more pronounce in high- $f_{SW}$  system, as  $t_{DT}$  takes up a larger fraction of  $t_{SW}$ . Although  $t_{V\Delta}$ 's are much shorter than  $t_{DT},\,v_{IV(SW)}$  can overwhelm  $\Delta d_E$  in high-voltage systems, as it contains  $v_I$  and  $v_O$  while the others are divided by  $v_E'+v_D'$ .

#### C. Loading Effect

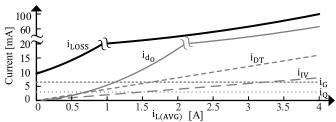

Previous subsections only considered the losses that alter  $v_L$ . Some losses do not change  $v_L$ , but effectively diverge current away from the output node or the load:

$$i_{LD(EFF)} = i_{LOSS} + i_{LD} = i_{Q} + i_{G} + i_{d_{Q}} + i_{DT} + i_{IV} + i_{LD}.$$

(15)

$i_Q$  is the quiescent current drawn from  $v_O$ , and  $i_G$  denotes the gate-drive current, or the amount of charge transferred to gate capacitance  $C_G$  by  $v_O$  over each  $t_{SW}$ :

$$i_G = \frac{P_G}{v_O} = \frac{C_G v_O}{t_{SW}}.$$

(16)

For boost and buck-boost, whose  $i_0$  is a  $1 - d_E$  fraction of  $i_{L(AVG)}$ , a higher  $d_E$  would result in a decrease in available  $i_{LD}$ :

$$i_{d_O} = i_{L(AVG)}(d_O' - d_O) = \Delta d_E i_{L(AVG)}|_{BSBB}.$$

(17)

Additionally, in each  $t_{DT}$ , some forward recovery charge  $q_{FR}$ , which is proportional to forward transit time  $\tau_F$ , is trapped in  $D_0$  that could have been supplied to the load:

$$i_{DT} = \frac{2q_{FR}}{t_{SW}} \bigg|_{BS,BB} \approx \frac{2\tau_{F}i_{L(AVG)}}{t_{SW}} \bigg|_{BS,BB}.$$

(18)

Referring to Fig. 11, it can also be seen that  $M_{EG}$  starts steering current away from the output  $t_{I(E)}$  before it closes and starts feeding the output  $t_{V(D)} + t_{I(D)}$  later than it is supposed to. Across  $t_I$ 's,  $i_{DS}$  rises or falls roughly quadratically. The output current taken away during IV overlap is then:

$$i_{IV} = \frac{q_{EG(IV)}}{t_{SW}} \approx \left(t_{V,EG(D)} + \frac{t_{I,EG(D)}}{3} + \frac{t_{I,EG(E)}}{3}\right) \left(\frac{i_{L(AVG)}}{t_{SW}}\right). (19)$$

Fig. 11 shows the trend of individual contribution and the total loading current  $i_{LOSS}$  across  $i_{L(AVG)}$ . Both  $i_{DT}$  and  $i_{IV}$  increase linearly with  $i_{L(AVG)}$ , while  $i_{dO}$  has both linear and quadratic components since  $\Delta d_E$  also increases with  $i_{L(AVG)}$ .

Fig. 11. Calculated loading effects.

#### V. MAXIMUM DC-DC CONVERSION

As discussed,  $d_E'$  is a relationship between  $v_E'$  and  $v_D'$ , and can be derived from  $d_E$  and  $\Delta d_E$ . In other words, a lossy SLPS operating at  $d_E$  can be reflected into an ideal SLPS operating at  $d_E'$  with the same  $v_E'$  and  $v_D'$ , or  $v_I$  and  $v_O$  as Table I shows. When the actual system operates at its delay-limited  $d_{MIN}$ , the imaginary ideal system has:

$$d_{MIN}' = d_{E/D(MIN)} - \Delta d_{E/D} = d_{MIN} \mp \Delta d_{E}. \tag{20}$$

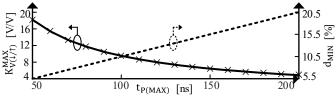

From (4),  $K_{V(\downarrow/\uparrow)}^{MAX}$  can be found and it is also the maximum conversion ratio of the actual, lossy system between identical  $v_I$  and  $v_O$  as the equivalent ideal system. It is worth noting that higher delay-limited  $d_{MIN}$  always lowers  $K_{V(\downarrow/\uparrow)}^{MAX}$ . Fig.12 shows the trend of decreasing  $K_{V(\downarrow/\uparrow)}^{MAX}$  with higher  $t_{P(MAX)}$  and  $d_{MIN}$ .

Fig. 12. Simulated maximum conversion ratio respect to delay.

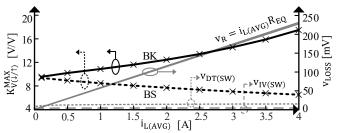

Loss-induced  $\Delta d_E$ , however, extends  $K_{V(1)}^{MAX}$  and reduces  $K_{V(\uparrow)}^{MAX}$  as (20) and (4) show. It aligns with the intuition that losses reduce voltage along the direction of current flow, favoring voltage step-down applications and countering step-up applications. Fig. 13 shows  $K_{V(\downarrow\uparrow\uparrow)}^{MAX}$  of a buck and a boost converter and their losses contributing to  $\Delta d_E$  across  $i_{L(AVG)}$ .

Fig. 13. Simulated buck and boost maximum conversion ratio.

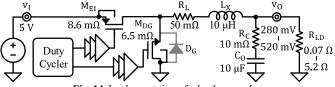

# A. Buck Example

The buck converter example in Fig.14 is supplied by a USB and operates at a  $f_{SW}$  of 1 MHz with a 10 ns  $t_{DT}$ . Its duty cycler has  $t_P^+$  of 100 ns and  $t_P^-$  of 110 ns, while the drivers have a  $t_{P\Delta}$  of 5 ns. At conversion limit,  $d_{E(MIN)}$  is 10.5 %, and  $R_{EQ}$  exhibited is 56.7 m $\Omega$ . Simulated with SPICE,  $K_{V(BK)}^{MAX}$  rises from 9.6 to 17.5 V/V across 0.1 – 4 A of  $i_{L(AVG)}$  as Fig.13 shows. When the power stage is replaced with lossless components and duty cycler's  $t_P$  varies, Fig.12 shows simulated  $K_{V(BK)}^{MAX}$ .

Fig. 14. Implementation of a buck example

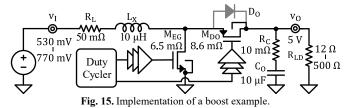

# B. Boost Example

The boost example in Fig.15 supplies a USB load and operates with the same  $f_{SW}$ ,  $t_{DT}$ , and delays. At conversion limit,  $d_{D(MIN)}$  is 10.5 % and  $R_{EQ}$  is 57.7 m $\Omega.$   $K_{V(BS)}^{MAX}$  falls from 9.4 to 6.5 V/V across  $i_{L(AVG)}$  as Fig.13 shows. Fig.12 shows  $K_{V(BS)}^{MAX}$  when the power stage is lossless and duty cycler's  $t_{P}$  varies.

VI. Conclusions

This paper comprehensively analyzes the factors affecting the maximum DC–DC conversion in SLPS. By lumping the impact of losses into a shift from delay-limited minimum duty cycle, an actual system can be reflected into an ideal equivalence, where the maximum conversion can be easily determined. The minimum duty cycle is largely set by the longest single-component delay, higher of which lowers achievable conversion ratio. Resistance, dead time, and IV overlap cause the duty cycle shift, which extends the maximum conversion in voltage step-down applications but reduces it in step-up. With the derivations and insights presented, designers can now assess the feasibility of using SLPS in high conversion applications.

#### ACKNOWLEDGMENT

The authors thank Analog Devices, Inc. (ADI) for sponsoring this research and Dr. Hua Chen for his support and advice.

#### REFERENCES

- B.-R. Lin, J.-J. Chen, and F.-Y. Hsieh, "Analysis and implementation of a bidirectional converter with high conversion ratio," in 2008 IEEE International Conference on Industrial Technology, 2008, pp. 1–6.

- [2] Y. Wang, Y. Qiu, Q. Bian, Y. Guan, and D. Xu, "A Single Switch Quadratic Boost High Step Up DC–DC Converter," *IEEE Transactions* on *Industrial Electronics*, vol. 66, no. 6, pp. 4387–4397, 2019.

- [3] V.-C. Nguyen, H. Cha, D.-V. Bui, and B. Choi, "Modified Double-Dual-Boost High-Conversion-Ratio DC–DC Converter With Common Ground and Low-Side Gate Driving," *IEEE Trans Power Electron*, vol. 37, no. 5, pp. 4952–4956, 2022.

- [4] P. S. Shenoy, M. Amaro, J. Morroni, and D. Freeman, "Comparison of a Buck Converter and a Series Capacitor Buck Converter for High-Frequency, High-Conversion-Ratio Voltage Regulators," *IEEE Trans Power Electron*, vol. 31, no. 10, pp. 7006–7015, 2016.

- [5] C. Wang, Y. Lu, M. Huang, and R. P. Martins, "A Two-Phase Three-Level Buck Converter With Cross-Connected Flying Capacitors for Inductor Current Balancing," *IEEE Trans Power Electron*, vol. 36, no. 12, pp. 13855–13866, 2021.

- [6] J. Ding, S. Zhao, S. Gao, and H. Yin, "A Single-Switch High Step-Up DC-DC Converter Based on Three-Winding Coupled Inductor and Pump Capacitor Unit," *IEEE Trans Power Electron*, vol. 37, no. 3, pp. 3053– 3061, 2022.

- [7] C. L. Narayana, H. M. Suryawanshi, P. Nachankar, P. Vijaya Vardhan Reddy, and D. Govind, "A Quintupler Boost High Conversion Gain Soft-Switched Converter for DC Microgrid," *IEEE Transactions on Circuits* and Systems II: Express Briefs, vol. 69, no. 3, pp. 1287–1291, 2022.

- [8] Y.-A. Lin, S.-Y. Li, Z.-L. Huang, C.-S, Huang, C.-H. Liang, K.-S. Chang, K.-C. Chung, K.-H. Chen, Y.-H. Lin, S.-R. Lin, and T.-Y. Tsai, "A High Conversion Ratio and 97.4% High Efficiency Three-Switch Boost Converter With Duty-Dependent Charge Topology for 1.2-A High Driving Current and 20% Reduction of Inductor DC Current in MiniLED Applications," *IEEE J Solid-State Circuits*, vol. 57, no. 6, pp. 1877–1887, 2022.

- [9] R. D. Middlebrook, "Transformerless DC-to-DC converters with large conversion ratios," *IEEE Trans Power Electron*, vol. 3, no. 4, pp. 484– 488, 1988.

- [10] E. H. Ismail, M. A. Al-Saffar, A. J. Sabzali, and A. A. Fardoun, "A Family of Single-Switch PWM Converters With High Step-Up Conversion Ratio," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 55, no. 4, pp. 1159–1171, 2008.

- [11] K. Wei, Y. Ramadass, and D. B. Ma, "Direct 12V/24V-to-1V Tri-State Double Step-Down Power Converter With Online VCF Rebalancing and In-Situ Precharge Rate Regulation," *IEEE J Solid-State Circuits*, vol. 56, no. 8, pp. 2416–2426, 2021.

- [12] L. Qin, T. Qian, J. L. Soon, W. Hassan, M. Tian, L. Zhou, and L. Ren, "Transformerless High-Gain Three-Port Converter With Low Voltage

- Stress and Reduced Switches for Standalone PV Systems," *IEEE Trans Power Electron*, vol. 37, no. 11, pp. 13468–13483, 2022.

- [13] Y. Lei and R. C. N. Pilawa-Podgurski, "Soft-charging operation of switched-capacitor DC-DC converters with an inductive load," in 2014 IEEE Applied Power Electronics Conference and Exposition - APEC 2014, 2014, pp. 2112–2119.

- [14] G.-S. Seo, R. Das, and H.-P. Le, "A 95%-Efficient 48V-to-1V/10A VRM Hybrid Converter Using Interleaved Dual Inductors," in 2018 IEEE Energy Conversion Congress and Exposition (ECCE), 2018, pp. 3825–3830.

- [15] Z. Ye, Y. Lei, and R. C. N. Pilawa-Podgurski, "A 48-to-12 V Cascaded Resonant Switched-Capacitor Converter for Data Centers with 99% Peak Efficiency and 2500 W/in3 Power Density," in 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), 2019, pp. 13–18.

- [16] N. Pal, A. Fish, W. McIntyre, N. Griesert, G. Winter, T. Eichhorn, R. Pilawa-Podgurski, and P. K. Hanumolu, "A 91.15% Efficient 2.3–5-V Input 10–35-V Output Hybrid Boost Converter for LED-Driver Applications," *IEEE J Solid-State Circuits*, vol. 56, no. 11, pp. 3499–3510, 2021.

- [17] H. Cao, X. Yang, C. Xue, L. He, Z. Tan, M. Zhao, Y. Ding, W. Li, and W. Qu, "A 12-Level Series-Capacitor 48-1V DC–DC Converter With On-Chip Switch and GaN Hybrid Power Conversion," *IEEE J Solid-State Circuits*, vol. 56, no. 12, pp. 3628–3638, 2021.

- [18] X. Hu, P. Ma, J. Wang, and G. Tan, "A Hybrid Cascaded DC–DC Boost Converter With Ripple Reduction and Large Conversion Ratio," *IEEE J Emerg Sel Top Power Electron*, vol. 8, no. 1, pp. 761–770, 2020.

- [19] R. Beiranvand and S. H. Sangani, "A Family of Interleaved High Step-Up DC-DC Converters by Integrating a Voltage Multiplier and an Active Clamp Circuits," *IEEE Trans Power Electron*, vol. 37, no. 7, pp. 8001–8014, 2022.

- [20] R. D. Middlebrook and S. Cuk, "A general unified approach to modelling switching-converter power stages," in 1976 IEEE Power Electronics Specialists Conference, 1976, pp. 18–34.

- [21] S. Akkihal and M. W. Thompson, "Generalized switched inductor model (GSIM): accounting for conduction losses," *IEEE Trans Aerosp Electron Syst*, vol. 38, no. 2, pp. 681–687, 2002.

- [22] A. Davoudi and J. Jatskevich, "State-space averaging of switched-inductor-cell for PWM dc-dc converters considering conduction losses in both operational modes," in 2006 IEEE International Symposium on Circuits and Systems, 2006.

- [23] P. S. Shenoy, M. Amaro, J. Morroni, and D. Freeman, "Comparison of a Buck Converter and a Series Capacitor Buck Converter for High-Frequency, High-Conversion-Ratio Voltage Regulators," *IEEE Trans Power Electron*, vol. 31, no. 10, pp. 7006–7015, 2016.

- [24] A. Ayachit and M. K. Kazimierczuk, "Averaged Small-Signal Model of PWM DC-DC Converters in CCM Including Switching Power Loss," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 66, no. 2, pp. 262–266, 2019.