# High-PSR LDOs:

# Variations, Improvements, and Best Compromise

Avinash Dinesh Shylaja and Gabriel A. Rincón-Mora, *Fellow, IEEE*Georgia Institute of Technology, Atlanta, Georgia 30332 U.S.A.

E-Mail: Avinash.DineshShylaja@analog.com and Rincon-Mora@gatech.edu

Abstract— Low-Dropout Regulators (LDOs) are used to power noise sensitive applications. Power Supply Rejection (PSR) is a performance metric that measures the LDO's ability to reject noise. Improving PSR has been the focus of many research groups. However, the state of the art does not recognize the best PSR enhancement schemes and collate them under comparable grounds. Further, the pass transistor's diode connection (through the Gate-Drain capacitance) impacts the PSR, and this effect is not quantified in the state of the art. This research aims to bridge these gaps first by explicating the constitution of a high PSR LDO. Then, the impact of the pass transistor's parasitics on PSR are quantified. Following this, the best state of the art PSR enhancement schemes are analyzed and simulated over a high-PSR core under similar conditions. This study reveals the strengths and limitations of each scheme, which unfolds each technique's applications. Results convey that the LDO Filter yields the best PSR improvement at low frequencies, Series feedback at mid frequencies, and RC filter at high frequencies. Assessment concludes that Series Feedback provides the best compromise with respect to PSR enhancement.

Index Terms—Analog, LDO, Linear Regulators, Power supply rejection (PSR), SPICE

# I. LDOs In Analog Systems

Supplying and regulating power is fundamental to the operation of electric systems. The wide range of applications from Portable electronics, Defense applications, microsensors, Automotive electronics, etc. cannot sustain themselves without energy, and cannot function without a stable power supply [1].

Fig. 1: Typical Power-Supply System.

Switching regulators (SL) efficiently regulate power but have limited bandwidths, typically around 370 kHz [2]. They suffer from poor load dump responses, causing the supply voltage to droop in the event of a load step. SLs have large ripple at their outputs, which manifests as Power Supply noise. Digital loads (logic gates) are not very sensitive to such noise and can function optimally under such supply conditions. Analog loads such as ADCs, PLLs, Amplifiers, and Mixers are susceptible to supply ripple and require low noise power supplies.

In typical applications, a low-dropout regulator (LDO) is used in series with SLs to reject noise and provide a clean regulated voltage [1]. Characterized with higher bandwidths, LDOs respond faster to load disturbances, yielding smaller voltage droops in the event of load steps. The LDO's regulated output can be used to power noise sensitive Analog loads. PSR

is a measure of how much input ripple is suppressed by the LDO. Modern applications like medical imaging demand high PSR (>50 dB) [3], especially in mid frequencies (0.1–1 MHz), where SLs switch and induce noise. This has motivated researchers to investigate techniques to enhance the PSR of LDOs.

The State of the art presents numerous techniques to improve the PSR of LDOs [4-11], but fails to compare the best techniques under similar conditions and operating points. The State of the art also fails to establish the grounds on which LDOs achieve the best PSR. The parasitic gate-drain capacitance which diode connects the pass transistor can impact PSR even in the low-mid frequency range. [12] recognizes the noise coupling effects due to parasitics, but does not quantify how it impacts the PSR across frequency. This work aims to bridge this gap by quantifying these effects both mathematically and graphically.

The purpose of this research is to first recognize the design factors affecting PSR and establish a high-PSR core LDO. This is covered in Section II. Sections III and IV present the best State of the art techniques that improve PSR. These techniques are applied as layers of concepts over the established core, and SPICE simulations reveal the PSR improvements. The highlighted strengths and limitations assist in assessing the conditions under which the said techniques offer maximum benefits. Section V compares the techniques discussed in this work, followed by Conclusions in Section VI.

# II. HIGH-PSR CORE

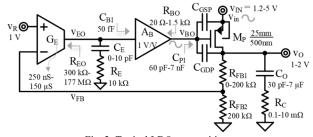

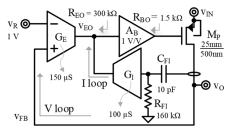

An LDO with high PSR is essential to reject supply noise generated by SLs. Fig. 2 depicts a typical LDO consisting of an Error Transconductor ( $G_E$ ) and a low output impedance Buffer ( $A_B$ ) that close a negative feedback loop around pass transistor  $M_P$ . If this loop is stabilized, the output voltage ( $v_O$ ) is established as a function of the reference voltage ( $v_R$ ) and the feedback resistors ( $R_{FB1}$ ,  $R_{FB2}$ ). Implementing  $M_P$  using PMOS transistors results in low dropout voltages when compared with NMOS pass transistors. Further, a replica LDO topology [13] offers a more predictable stability response, but suffers from poor load regulation due to the unregulated loading [14]. Thus, a single transistor  $M_P$  is suitable.

Fig. 2: Typical LDO composition.

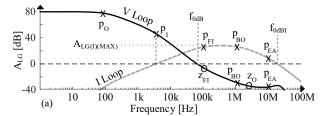

# A. Loop Gain

The LDOs loop gain depicted in Fig. 3 can be analyzed by considering the poles/zeroes established at each node. Each node contributes to a pole whose frequency is given by the RC frequency associated with that node, giving rise to poles  $p_E$ ,  $p_{BO}$ , and p<sub>O</sub>. Further, the current limiting effects of R<sub>C</sub> (ESR of C<sub>O</sub>) and resistance  $R_E$  establish zeroes ( $z_E$ ,  $z_O$ ) with their respective capacitances that boost phase margins. The DC loop gain (A<sub>LG0</sub>) and the output impedance (R<sub>O</sub>) can be expressed as:

$$A_{LGO} = G_E R_{EO} A_B g_{mP} R_O \left( \frac{R_{FB2}}{R_{FB1} + R_{FB2}} \right),$$

(1)

$$R_{O} = (R_{FB1} + R_{FB2})||r_{dsP}.$$

$$A_{LG0}$$

$$P_{DOE}$$

$$P_{DOE}$$

$$P_{BO}$$

$$Z_{O/E}$$

$$P_{E/O}$$

$$P_{E/O}$$

$$P_{E/O}$$

Frequency [Hz] Fig. 3: LDO's Loop gain plot depicting poles and zeroes.

With a single pole roll-off, the unity gain bandwidth ( $f_{0dB}$ ) is the product of the DC loop gain and the location of the dominant pole p<sub>D</sub>. Depending on the location of the dominant pole, LDO designs could be either output stabilized ( $p_D = p_O$ ) [15,16] or internally stabilized ( $p_D = p_E$ ) [17,18]:

$$f_{\text{odB}} = A_{\text{LG0}} p_{\text{D}} |_{p_{\text{D}} = p_{\text{E}} \text{ (or) } p_{\text{O}}}.$$

(3)

The PSR performance of output and internally stabilized designs are vastly different, and this will be evident in the following sub-sections.

# Gate Ripple

Since M<sub>P</sub> is a PMOS, and the input ripple is connected to M<sub>P</sub>'s source, it is desired to replicate this ripple at M<sub>P</sub>'s gate to ensure that there is no small signal source-gate voltage. This ensures that there is no noise injection through the g<sub>m</sub> currents of M<sub>P</sub>. There are two ways of replicating the input ripple at the gate:

#### 1. Feed-Forward path

The input ripple is injected to the gate of M<sub>P</sub> by using a feedforward path [8,9] as shown in Fig. 4.

Fig. 4: Supply Noise replication through Feed-fw.

Transconductor G<sub>FF</sub> closes a negative feedback loop around M<sub>FF</sub>. This loop holds M<sub>FF</sub>'s source at ac ground, generating feed-forward current iff. This feed-fw current is injected into the output of the buffer, and under the condition that R<sub>X</sub>=R<sub>BO</sub>, impresses a voltage at v<sub>bo</sub> given by:

$$v_{bo} = i_{ff} R_{BO} = \left(\frac{v_{in}}{R_X}\right) R_{BO} = v_{in}.$$

(4)

The bandwidth of this loop (fB) should be much greater than the Buffer pole pBO to ensure that the feed-forward path does not hinder the ripple replication until p<sub>BO</sub> shunts.

$$f_{B} = A_{BLG0}p_{G} \gg p_{BO}|_{p_{G} = \frac{1}{2\pi R_{BP}C_{BP}}}$$

(5)

#### Current mirror

(2)

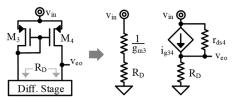

The other method to replicate supply ripple is to utilize the current mirror in the error transconductor (G<sub>E</sub>) [1]. Fig. 5 shows the Differential stage of the error transconductor feeding a Ptype current mirror, with its equivalent small signal model.

Fig. 5: Supply Noise replication through current mirrors

The fraction of input ripple (vin) reaching the output of the error transconductor (veo) is denoted by ADD, and can be calculated by applying superposition:

$$A_{DD} = \frac{v_{eo}}{v_{in}} = \frac{v_{in}R_D}{R_D + r_{ds4}} + i_{g34}(R_D||r_{ds4}), \qquad (6)$$

$$\frac{v_{eo}}{v_{in}} = \frac{v_{in}R_D}{R_D + r_{ds4}} + \left(\frac{v_{in}}{1/g_{m3} + R_D}\right)(R_D||r_{ds4}) \approx 1.$$

(7)

This indicates that the P-type mirror replicates the positive supply ripple at v<sub>eo</sub> and this ripple can propagate to the gate of M<sub>P</sub> through the buffer A<sub>B</sub>. This technique is superior to the feedfw technique since it eliminates the need for additional circuitry, that imposes its own bandwidth and gain constrains, in addition to power consumption. Thus, the designs discussed in this work will use a P-type mirror to replicate supply ripple.

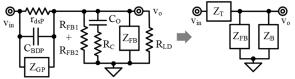

PSR is the inability to amplify supply noise and can be analyzed as the reciprocal of the supply gain  $(A_{IN})$  [19]. Fig. 6 depicts the voltage divider model of supply gain, where the supply gain is the fraction of the input ripple that reaches the output.

$$A_{IN} = \frac{1}{PSR} = \frac{v_o}{v_{in}} = \frac{Z_{FB}||Z_B}{(Z_{FB}||Z_B) + Z_T}. \tag{8}$$

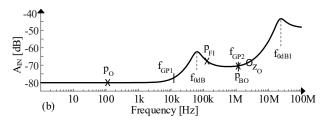

Z<sub>GP</sub> factors the noise coupling effects of M<sub>P</sub>'s diode connection through C<sub>GDP</sub>. From the perspective of the output node, the network of C<sub>GSP</sub>, C<sub>GDP</sub>, and R<sub>BO</sub> presents a voltage divided 1/g<sub>mP</sub> impedance to the supply that decreases with operating frequency (f<sub>O</sub>). This impedance overwhelms r<sub>dsP</sub> at frequency  $f_{GP1}$ .  $Z_{GP}$  keeps decreasing until  $f_{GP2}$  where the effects of  $R_{BO}$  disappear, and  $Z_{GP}$  flattens out as per (11). Fig. 7(a) depicts the effective impedance  $Z_T$  as a function of frequency.

$$Z_{GP} = \frac{1}{G_{P}} = \frac{\left(\frac{1}{sC_{GSP}}||R_{BO}\right) + \frac{1}{sC_{GDP}}}{g_{mP}\left(\frac{1}{sC_{GSP}}||R_{BO}\right)}, \qquad (9)$$

$$Z_{GP}|_{f_{O} \ge \frac{1}{2\pi R_{BO}[C_{GDP}(g_{mP}r_{dSP}-1)-C_{GSP}]} = f_{GP1}} \le r_{dsP}, \qquad (10)$$

$$Z_{GP}|_{f_0 \ge \frac{1}{2\pi R_{RO}[C_{GDP}(g_{mP}r_{dsP}-1)-C_{GSP}]} = f_{GP1}} \le r_{dsP},$$

(10)

$$Z_{GP}|_{f_O \ge \frac{1}{2\pi R_{BO}(C_{GSP} + C_{GDP})} = f_{GP2}} \approx \frac{C_{GDP} + C_{GSP}}{g_{mP}C_{GDP}},$$

(11)

$$Z_{T} = r_{dsP} \left| \left| \frac{1}{sC_{BDP}} \right| \right| Z_{GP}, \qquad (12)$$

$$Z_B = (R_{FB1} + R_{FB2}) || \left( \frac{1}{sC_0} + R_C \right) || (R_{LD}),$$

(13)

$$Z_{FB} = \frac{1}{G_{LG}} = \frac{1}{G_E R_{EO} A_B g_{mP}}.$$

(14)

Z<sub>FB</sub> captures the effects of shunt feedback at the output of the LDO. At low frequencies, Z<sub>FB</sub> dominates the parallel combination described by (8), resulting in very low A<sub>IN</sub> (and thus, high PSR). As f<sub>0dB</sub> is approached, the effects of shunt feedback disappear, and the supply gain is a function of the external filter components connected at the LDOs output.

Fig. 7(b) shows the supply gain plots of internally and output stabilized LDOs across frequency. Crossing the dominant pole of the output stabilized design ( $p_0$ ) has no effect on  $Z_{FB}$  as per (14), and  $A_{IN}$  remains constant. However, crossing the dominant pole of the internally stabilized design ( $p_E$ ') increases  $Z_{FB}$ , and due to this  $A_{IN}$  increases beyond  $p_E$ '.

Fig. 7: (a)  $Z_T$  vs frequency, (b)  $A_{IN}$  for internally and output stabilized LDOs.

Beyond  $f_{GP1}$ , the decreasing  $Z_{GP}$  overwhelms  $r_{dsP}$ , and dominates the parallel combination. This couples noise to the output node, and the supply gain increases as shown in Fig. 7(b). This effect disappears at  $f_{GP2}$ , beyond which the noise  $Z_{GP}$  couples is constant. Pushing  $f_{GP1}$  to higher frequencies helps improve  $A_{IN}$ . Without parasitic coupling, this effect is not seen. Instead,  $Z_{CO}$  overwhelms  $Z_{FB}$  and improves  $A_{IN}$  near  $f_{0dB}$ .

Beyond  $f_{GP2}$  and  $f_{0dB}$ , the shunted  $C_O$  ( $p_O$ ) decreases  $A_{IN}$  until  $z_O$ , at which point  $R_C$ 's current limiting effects flatten  $A_{IN}$ . At  $f_{0dB}$ , the output stabilized design offers much lower  $A_{IN}$  since  $p_O$  has shunted, and thus the supply noise has a low impedance path to ground. However, the output pole ( $p_O$ ') of the internally stabilized design has not shunted at  $f_{0dB}$ , and hence offers a higher  $A_{IN}$ . Thus, an output stabilized design is desired.

Thus, the established high-PSR core is an output stabilized design with the gate ripple replicated with the help of the P-type current mirror in the error transconductor. This core establishes the grounds on which the PSR enhancement techniques discussed in the next sections can be compared.

# III. PRE-FILTERED INPUT

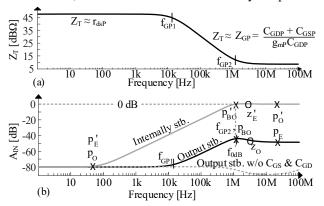

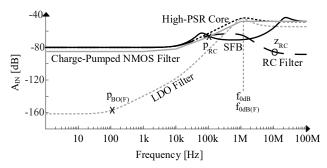

In this section, three techniques are presented which improve the PSR of the LDO. These techniques are applied as layers of concepts over the core that was established in the previous section. Fig. 8 shows the schematics of the three pre-filter techniques, and Fig. 11 shows the simulations of the improved supply gains  $(A_{\rm IN})$  of the LDO upon applying these techniques.

Fig. 8: (a) RC, (b) LDO, and (c) CP-NMOS Pre-Filter.

#### A. RC Filter

This technique uses a simple RC filter to clean up the supply ripple before it reaches the input of the LDO [4]. The cutoff frequency of this filter adds a pole in the supply gain response of the high-PSR core as shown in Fig. 11. The cutoff frequency is chosen to be a decade below  $f_{0dB}$  of the core:

$$p_{RC} = \frac{1}{2\pi R_{\rm F} C_{\rm F}} = \frac{f_{\rm 0dB}}{10}.$$

(15)

A low resistance of  $R_F$  is desired to minimize static power. This yields a large off-chip capacitor of 1.6  $\mu F$  for  $C_F$ , which is a limitation. The ESR of  $C_F$  establishes a zero ( $z_{RC}$ ) that flattens the  $A_{IN}$  response, and this limits the maximum improvement attainable. The other limitation relates to headroom- the voltage drop across  $R_F$  adds with the dropout voltage of the core, increasing effective dropout ( $V_{DO}$ ).

#### B. LDO Filter

This technique cascades two LDOs in series [4]. The filtering regulator LDO<sub>F</sub> shields the core from the supply ripple. LDO<sub>F</sub> can be made on-chip, thus requiring an internally stabilized design. This can be designed as a Transconductor ( $G_{E(F)}$ ) closing a negative feedback loop around pass transistor  $M_{P(F)}$ , establishing the dominant pole at the gate of  $M_{P(F)}$  ( $p_{BO(F)}$ ). The unity gain frequency ( $f_{0dB(F)}$ ) of LDO<sub>F</sub> is:

$$f_{\text{0dB(F)}} = \frac{G_{E(F)}g_{mP(F)}R_{O(F)}}{2\pi C_{PI(F)}}.$$

(16)

The design can be approached taking care that  $f_{0dB(F)}$  and  $A_{LG0(F)}$  should be at least equal to the core's parameters. This ensures that  $LDO_F$  effectively shields the core at least until  $f_{0dB}$  is reached. These yield  $G_{E(F)}$  of  $200~\mu S$  and  $R_{EO(F)}$  of  $250~k\Omega.$  As seen in Fig. 11, this technique drastically improves the supply gain at lower frequencies. Being an internally stabilized design,  $A_{IN}$  of  $LDO_F$  degrades beyond the dominant pole  $p_{BO(F)}$ , thus degrading the supply gain of the cascaded pair.

Near and beyond  $f_{0dB(F)}$ , this technique provides little to no improvement in  $A_{\rm IN}$ . Increasing  $f_{0dB(F)}$  to orders of magnitude higher than  $f_{0dB}$  would present its own design challenges as parasitic poles would jeopardize the stability of LDO<sub>F</sub>. Since two LDOs are in series, this technique also increases dropout.

## C. Charge-Pumped NMOS Filter

In [5], an NMOS device was used to cascode the LDO. The gate of the NMOS was biased using an RC filter connected to the input supply. This source follower configuration shields the core from input ripple similar to the RC filter discussed earlier. The RC filter does not dissipate static power, so the resistance can be made large. The drawback is that the dropout is a Gate-Source voltage (500-600mV) above the dropout of the core.

An improvement to this technique is presented in [6]. As shown in Fig. 8(c), a Charge pump of N stages is used to boost the gate drive of the cascode transistor  $M_{\rm C}$ . The effective dropout voltage is a  $V_{\rm DSC(SAT)}$  above the dropout of the core.  $R_{\rm CPF}$  and  $C_{\rm CPF}$  maintain the role of the RC filter to clean up supply ripple. To keep  $M_{\rm C}$  in the saturated inversion region,

$$V_{GSC} = (N + 1)V_{IN} - 2NV_{Diode} - V_{IN}',$$

(17)

$$V_{DSC} = V_{IN} - V_{IN}' \ge V_{GSC} - V_{TN0},$$

(18)

$$V_{\rm IN} < 2V_{\rm Diode} + \frac{V_{\rm TN0}}{N}.\tag{19}$$

This imposes a maximum input voltage constrain. If  $V_{\rm IN}$  increases beyond this limit,  $M_{\rm C}$  enters linear region, and the noise from  $V_{\rm IN}$  directly couples to the input of the LDO. Thus, a single stage charge pump is chosen. Width of  $M_{\rm C}$  can be designed from choosing  $V_{\rm DSC(SAT)}$  of 250 mV that yields  $W_{\rm C}$  of 15mm. The pole of the RC filter can be chosen to be a decade below  $f_{\rm 0dB}$ , similar to (15).

The supply gain simulations reveal that while the diodes in the charge pump and the RC filter do filter the input ripple, the input ripple couples to the gate of  $M_{\rm C}$  ( $v_{\rm gc}$ ) through the large gate-drain capacitance ( $C_{\rm GDC}$ ) of  $M_{\rm C}$ :

$$v_{gc} = \frac{C_{GDC}}{C_{GDC} + C_{CP}}.$$

(20)

$M_{\rm C}$  has a large width and consequently a large  $C_{\rm GDC}$  of 10pF. This capacitive coupling leads to a large fraction of input ripple being coupled to  $v_{\rm gc}$ , and source follower  $M_{\rm CP}$  replicates this ripple to the input of the core. This yields a minor supply gain improvement (5-6 dB), as depicted by Fig. 11.

The limitations stem from the noise coupling nature, making it unsuitable for high load current applications. Larger loads demand a larger  $W_C$ , which increases  $C_{GDC}$  (and noise coupling), thus decreasing the improvement in  $A_{IN}$ . The other limitation is the maximum input voltage constrain induced by the Charge pump mechanism. Finally, the dropout is increased by  $V_{DSC(SAT)}$ . [6] were able to obtain 30 dB of improvement using this technique, reaching 70 dB of PSR at DC. This high improvement is mainly due to the lower target load current.

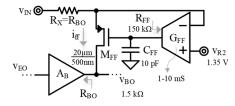

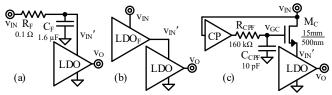

### IV. SERIES FEEDBACK

The Series feedback (SFB) technique [7] can improve supply gain at mid-high frequencies, without dissipating additional ohmic losses or increasing  $V_{DO}$ . As seen from Fig. 6, lower  $A_{IN}$  can be achieved either by decreasing  $Z_{FB}$ , or by increasing  $Z_{T}$ . The LDO's shunt feedback action already decreases  $Z_{FB}$  in the low-mid frequencies. Extending the frequency range where  $Z_{FB}$  remains low can compromise stability due to parasitic poles. This technique introduces a high frequency series sampling loop that increases the impedance presented to the supply  $(Z_T)$ . Fig. 9 depicts the LDO with series feedback.

Fig. 9: Series Feedback.

Transconductor  $G_I$  and the high pass filter  $(R_{FI}, C_{FI})$  close a series sampling loop (I loop) around  $M_P$ . Note that the series sampling action can be implemented with a mirror PMOS  $(M_P')$  that is scaled down in size, in series with a sense resistor.

The I loop gains maximum strength based on the cutoff frequency set by the high pass filter ( $p_{FI}$ ), chosen to be a decade below the core's unity gain frequency. The peak loop gain of the I-loop ( $A_{LGI(MAX)}$ ) is chosen to be 30, and is given by:

$$A_{LG(I)(MAX)} \approx G_I R_{EO}.$$

(21)

After attaining the peak value, the loop gain of the I-loop rolls off after  $p_{BO}$  shunts as shown in Fig. 10(a). The loop gain of the outer loop (V loop) that establishes  $v_{O}$  as a function of  $v_{REF}$  at low frequency is also shown. The 0-dB crossing point of the I loop creates a pole ( $p_{I}$ ) in the V loop, which affects  $f_{OdB}$  (60 kHz) and Phase Margin (40°) of the V loop.

Fig. 10(b) depicts the plot of  $A_{\rm IN}$  for the SFB LDO. Due to the effects of  $Z_{\rm GP}$ ,  $A_{\rm IN}$  increases beyond  $f_{\rm GP1}$  until  $f_{\rm 0dB}$ . Beyond  $f_{\rm 0dB}$ , the combined effects of the shunting output capacitor and the increasing strength of the I loop decreases  $A_{\rm IN}$ , resulting in a "peaking" effect around  $f_{\rm 0dB}$ . Once  $A_{\rm LG(I)(MAX)}$  is reached,  $A_{\rm IN}$  flattens. After  $p_{\rm BO}$  shunts,  $f_{\rm GP2}$  is reached and  $R_{\rm C}$  current limits  $C_{\rm O}$ ,  $A_{\rm IN}$  increases, and joins the core's response at  $f_{\rm 0dBI}$ .

Fig. 10: (a) Voltage and Current loop gains, (b) Supply gain of SFB LDO.

To compensate for the drop in  $f_{0dB}$ ,  $G_E$  would need to be raised proportionately to maintain the same  $f_{0dB}$  as the core. This would mean higher quiescent currents, which would impact the overall current efficiency of the LDO. This is not done in this work to maintain the same  $A_{LGO}$ . [7] were able to obtain 20 dB of improvement using this technique, reaching 50 dB of PSR around their unity gain frequency.

#### V. COMPARISON

This section presents a comparison of the various PSR enhancement techniques. Fig. 11 shows the  $A_{\rm IN}$  plots for each technique, and Table 1 provides a quantitative comparison. The LDO filter drastically improves PSR at low frequencies but starts degrading towards the mid-high frequency range. The RC filter utilizes a large off-chip capacitor to improve PSR at high frequencies. The CP-NMOS provides little improvement in PSR due to the noise coupling through parasitics of the large cascoding NMOS. Series-FB improves PSR in the mid-high frequency range without compromising  $V_{\rm DO}$ , but at the expense of reduced  $f_{\rm 0dB}$  and little quiescent power ( $P_{\rm GI}$ ) consumed by  $G_{\rm I}$ .

Fig. 11: Supply gain plots of the discussed PSR enhancement techniques.

# TABLE I: PSR COMPARISON

| Parameter    | High PSR<br>Core | RC<br>Filter | LDO Filter          | CP<br>NMOS        | Series<br>Feedback |

|--------------|------------------|--------------|---------------------|-------------------|--------------------|

| PSR(10 kHz)  | 78 dB            | 78 dB        | 118 dB              | 82 dB             | 78 dB              |

| PSR(100 kHz) | 62 dB            | 66 dB        | 82 dB               | 67 dB             | 66 dB              |

| PSR(1 MHz)   | 44 dB            | 64 dB        | 44 dB               | 48 dB             | 71 dB              |

| PSR(10 MHz)  | 48 dB            | 85 dB        | 54 dB               | 48 dB             | 57 dB              |

| PSR(100 MHz) | 48 dB            | 88 dB        | 54 dB               | 48 dB             | 48 dB              |

| $V_{DO}$     | 0.2 V            | 0.4 V        | 0.7 V               | 0.45 V            | 0.2 V              |

| Power        | _                | $+P_{RF}$    | $+ P_{LDO(F)}$      | + P <sub>CP</sub> | $+P_{GI}$          |

| Space        | _                | $+R_F, C_F$  | $M_{P(F)}+G_{E(F)}$ | + CP              | $G_I + M_P'$       |

\*Simulation results shown for same operating conditions.

Researchers have investigated techniques to improve PSR by bulk modulation [10,11]. Biasing the bulk terminal introduces substrate currents that contribute to power loss. Constrains exist to prevent the body diode from switching on. The solutions tend to complicate the circuit, and this increases Silicon area, cost, and test times while providing similar PSR improvements as the techniques previously discussed. For these reasons, these techniques have been excluded in this work.

Another area that has gained the attention of researchers is Digital LDOs [20, 21]. They use digital control to turn on a number of switches in a FET array to supply the load. The power transistors are driven to linear region; the supply ripple couples directly to the output. This makes digital LDOs exhibit poor PSR performance and have been excluded in this work.

# VI. CONCLUSIONS

This work establishes a high PSR core, investigating the effects of the pass transistor's diode connection which the state of the art did not account for. By analyzing and simulating the best PSR enhancement techniques in the state of the art, improvements in PSR are revealed, elucidating their potential use cases. The LDO filter provides the best PSR improvement at low frequencies, Series-FB at mid frequencies, and RC filter at high frequencies. Improving PSR (>25 dB) without sacrificing dropout and with little additional power consumption makes Series-feedback utilizing a PMOS current mirror the best compromise with respect to PSR enhancement. Charge pumped NMOS regulators operate in a source follower configuration, and will exhibit frequency spurs at the regulator's output near and around the Charge pump's frequency, making PMOS based LDOs with Series feedback superior in performance.

#### ACKNOWLEDGEMENT

The authors thank D. Kwon, A. Patel, T. Owen, M. Sekerli, and Analog Devices for their support and guidance.

### REFERENCES

- G.A. Rincón-Mora, Analog IC Design with Low-Dropout Regulators, McGraw-Hill, 2009.

- [2] C. J. Solis and G. A. Rincón-Mora, "Stability analysis & design of hysteretic current-mode switched-inductor buck DC-DC converters," 2013 IEEE 20th International Conference on Electronics, Circuits, and Systems (ICECS), pp. 811-814, Dec. 2013.

- [3] Analog Devices, "20V, 500mA, Ultralow Noise, Ultrahigh PSRR Linear Regulator," part LT3045.

- [4] V. Gupta and G.A. Rincon-Mora, "A low dropout, CMOS regulator with high PSR over wideband frequencies," *IEEE International Symposium on Circuits and Syst.*, vol. 5, pp. 4245-4248, Tokyo, Japan, May 2005.

- [5] J. M. Ingino, and V.R. von Kaenel, "A 4-GHz clock system for a high performance system-on-a-chip design," *IEEE Journal of Solid-State Circuits*, vol. 36, pp. 1693-1698, Nov. 2001.

- [6] V. Gupta and G. A. Rincón-Mora, "A 5 mA 0.6 μm CMOS Millercompensated LDO regulator with -27 dB worst-case power-supply rejection using 60 pF of on-chip capacitance," *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, pp. 520–521, Feb. 2007.

- [7] A. Patel and G. A. Rincón-Mora, "High power-supply-rejection (PSR) current-mode low-dropout (LDO) regulator," *IEEE trans. on Circuits and Syst. II*, vol. 57, no. 11, pp. 868-873, Nov. 2010.

- [8] K. Joshi, S. Manandhar and B. Bakkaloglu, "A 5.6 μA wide bandwidth, high power supply rejection linear low-dropout regulator with 68 dB of PSR up to 2 MHz," *IEEE Journal of Solid-State Circuits*, vol. 55, no. 8, pp.2151-2160, Aug. 2020.

- [9] M. El-Nozahi, A. Amer, J. Torres, K. Entesari and E. Sanchez-Sinencio, "High PSR low drop-out regulator with feed-forward ripple cancellation technique," *IEEE Journal of Solid-State Circuits*, vol. 45, no. 3, pp.565-577, Mar. 2010.

- [10] Y. Lim, J. Lee, S. Park, Y. Jo and J. Choi, "An external capacitorless low-dropout regulator with high PSR at all frequencies from 10 kHz to 1 GHz using an adaptive supply-ripple cancellation technique," *IEEE Journal of Solid-State Circuits*, vol. 53, no. 9, pp. 2675-2685.

- [11] F. Lavalle-Aviles, J. Torres and E. Sánchez-Sinencio, "A high power supply rejection and fast settling time capacitor-less LDO," *IEEE Transactions on Power Electronics*, vol. 34, no. 1, pp. 474-484, Jan. 2019.

- [12] C.J. Park; M. Onabajo; J. Silva-Martinez, "External Capacitor-Less Low Drop-Out Regulator With 25 dB Superior Power Supply Rejection in the 0.4-4 MHz Range," *IEEE Journal of Solid-State Circuits*, Vol.49, No.2, pp.486-501, Feb. 2014.

- [13] G. W. den Besten and B. Nauta, "Embedded 5 V-to-3.3 V voltage regulator for supplying digital IC's in 3.3 V CMOS technology,", *IEEE Journal of Solid-State Circuits*, vol. 33, no. 7, pp. 956-962, July 1998.

- [14] Y. Nan, C. Zhan, G. Wang, L. He and H. Li, "Replica-Based Low Drop-Out Voltage Regulator with Assistant Power Transistors for Digital VLSI Systems," 2018 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), 2018, pp. 6-9.

- [15] G.A. Rincon-Mora and P. E.Allen, "A low-voltage, low quiescent current, low drop-out regulator," *IEEE J. Solid-State Circuits*, vol. 33, no. 1, pp. 36–44, Jan. 1998.

- [16] C.-H. Huang, Y.-T. Ma, and W.-C. Liao, "Design of a low-voltage lowdropout regulator," *IEEE Trans. Very Large Scale Integr. (VLSI)* Syst., vol. 22, no. 6, pp. 1308–1313, Jun. 2014.

- [17] R. J. Milliken, J. Silva-Martinez, and E. Sánchez-Sinencio, "Full on-chip CMOS low-dropout voltage regulator," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 54, no. 9, pp. 1879–1890, Sep. 2007.

- [18] S. K. Lau, P. K. T. Mok and K. N. Leung, "A low-dropout regulator for SoC with Q-reduction," IEEE J. Solid-State Circuits, vol. 42, no. 3, pp. 658–664, Mar. 2007.

- [19] V. Gupta and G. A. Rincón-Mora, "Analysis and design of monolithic, high PSR, linear regulators for SoC applications," *IEEE Int. SOC Conf.*, Sep. 2004, pp. 311–315.

- [20] J. Silva-Martinez, X. Liu and D. Zhou, "Recent advances on linear low-dropout regulators," *IEEE trans. on Circuits and Syst. II*, vol. 68, no. 2, pp. 568-573, Feb. 2021.

- [21] M. Huang, Y. Lu and R. P. Martins, "Review of analog-assisted-digital and digital-assisted-analog low dropout regulators," *IEEE trans. on Circuits and Syst. II*, vol. 68, no. 1, pp. 24-29, Jan. 2021.