# Fast Energy-Harvesting TEG-Supplied Charging Regulator Microsystem

Tianyu Chang, and Gabriel A. Rincón-Mora, Fellow, IEEE

Abstract—This paper presents a fast hysteretic switched-inductor charging regulator (SLCR) microsystem. It is powered by onchip thermoelectric generators (TEGs) to supply Internet-of-Things (IoT) wireless microsensors. On-chip TEGs are appealing because they are 12-1400× smaller than off-chip ones. IoT sensors mostly idle in low-power mode and transmit data wirelessly only in high-power mode on demand. This requires CMOS SLCRs to respond quickly to abrupt load dumps caused by IoT sensors. State-of-the-art (SoA) SLCRs respond to load dumps in 100 µs-2.5 ms. This time duration amounts to a significant portion of the IoT sensor's data transmission time (500 μs-7 ms). This slow response time jeopardizes the quality of data transmission. This paper presents a fast hysteretic control that responds in 9.6 µs. This control adopts nested hysteretic architecture and requires only three comparators and simple combinational logics, which is appealing, considering the low power budget limited by on-chip TEGs. Moreover, this paper contributes detailed stability analysis, derives response time and accuracy and provides intuitive and accurate system design equations. Measured results of a 180-nm CMOS prototype validate that the proposed system shortens response time by 10-260× compared to the SoA.

Keywords—Switched inductor, charging regulator, fast, response time, stability, design, energy harvesting, thermoelectric, CMOS.

### I. POWERING IOT MICROSENSORS WITH CMOS TEGS

Internet-of-Things (IoT) wireless microsensors can save money, energy, and lives [1]. Because of volume constraints, tiny IoT sensors usually carry small onboard batteries. These tiny batteries carry limited energy and shorten IoT sensors' lifetimes. Recharging batteries manually is labor intensive since these sensors are usually deployed at hard-to-reach locations. One possible solution is harvesting thermal energy to supply IoT sensors [2]. A thermoelectric generator (TEG) converts thermal gradients to electricity, which can be used to supply IoT sensors.

Typical TEGs are made of bismuth telluride or lead telluride (Bi-/Pb-Te), which are difficult to integrate on chip. Thus, typical TEGs are off chip and bulky, occupying 9–42 cm<sup>2</sup> [3–6]. Because an IoT sensor can be as tiny as 1.5 mm<sup>3</sup> [7], using bulky centimeter-scale off-chip TEGs to power such tiny sensors is unacceptable.

State-of-the-art (SoA) TEGs can be integrated on chip using micro-electro-mechanical systems (MEMS) technology. On-chip TEGs are made of Si, poly-Si, or poly-SiGe, using CMOS or BiCMOS processes and MEMS post-processing [8–11]. They

Tianyu Chang is with Texas Instruments Incorporated, Dallas, TX, U.S.A. E-mail: t-chang3@ti.com.

Gabriel A. Rincón-Mora is with the School of Electrical and Computer Engineering, Georgia Institute of Technology, Atlanta, GA, U.S.A. E-mail: rincon-mora@satech.edu

This research is supported by Texas Instruments Incorporated.

occupy  $3-70 \text{ mm}^2$ , which is  $12-1400 \times \text{ smaller}$  than off-chip ones.

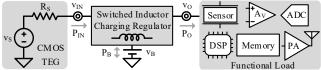

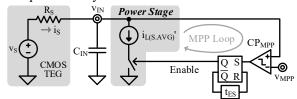

Unfortunately, the internal source resistance  $R_S$  of on-chip TEGs (shown in Fig. 1) is much higher than that of off-chip TEGs. On-chip TEG's  $R_S$  can be 0.7–1.3 M $\Omega$  [8–11], whereas off-chip TEG's  $R_S$  is 0.16-4  $\Omega$  [3–6]. This high  $R_S$  limits on-chip TEG's maximum available power  $P_{MPP}$  to 1.8–17 nW/°C² [8–11], which is 3300–22000× lower than that of off-chip ones. Table I compares on-chip and off-chip TEGs.  $v_S$  is the open-circuit source voltage provided by the TEG.

Fig. 1. A CMOS-TEG sourced microsystem.

While IoT sensors consume nanowatts (nW) [1] when sensing, they burn milliwatts (mW) [12] during data transmission [13–14]. Thus, when sensors idle, the CMOS switched inductor charging regulator (SLCR) in Fig. 1 draws input power  $P_{\rm IN}$  from the TEG and directs a fraction of  $P_{\rm IN}$  to supply load power  $P_{\rm O}$ . The SLCR charges battery  $v_{\rm B}$  with the remaining fraction of  $P_{\rm IN}$  to store this extra energy. When the sensor demands higher power during data transmission, the SLCR draws battery power  $P_{\rm B}$  from  $v_{\rm B}$  to supply the load. This load profile requires the SLCR to respond quickly to load dumps to secure proper sensor function.

Material Size  $[mm^2]$  On-Chip  $v_S$   $[mV/^{\circ}C]$   $R_S$   $[\Omega]$   $P_{MPP}$   $[W/^{\circ}C]$ Bi-Te 56 μ Bi-Sb-Te  $63 \times 63$ OFF 160 m 350 u 15 Bi-Te  $61 \times 71$ OFF 1.0  $400 \mu$ PbTe-BiTe 56 × 56 OFF 970 m 28 Poly-Si  $3 \times 3$ ON 160 1.3 M 4.9 n Poly-Si ON 700 k 8.0 n

250

900 k

760 k

17 n

1.8 n

ON

ON

TABLE I: COMPARISON OF ON-CHIP AND OFF-CHIP TEGS

Poly-SiGe

\* Estimates.

$11 \times 1.5$

\*14 × 5

Previous studies in [16–20] rarely report load dump responses. For those that do, reported response time  $t_R$  is 100  $\mu s-2.5$  ms [21–24]. This slow  $t_R$  amounts to a significant fraction of the duration of data transmission (0.5–7 ms [13–14]) and may jeopardize data quality. Moreover, prior arts rarely analyze control stability.

Thus, this paper presents a fast hysteretic SLCR microsystem achieving 9.6  $\mu$ s  $t_R$ . With detailed theory, this paper analyzes control stability, derives  $t_R$  and accuracy, and provides closed-form design equations. Moreover, in catering to the high  $R_S$  and low  $P_{MPP}$  of on-chip TEGs, this control employs only three comparators and combinational logics. This implies lower controller power for on-chip implementations. Contributions of this paper include the following:

- A fast hysteretic SLCR microsystem with 9.6-μs t<sub>R</sub>.

- 2) Stability, t<sub>R</sub>, and accuracy analysis with design equations.

- Extensive measurements verifying theory, design expressions, and transient performance.

Section II introduces the SLCR system and analyzes stability and t<sub>R</sub>. Sections III and IV derive system design equations and present measured performances. Section V concludes this paper.

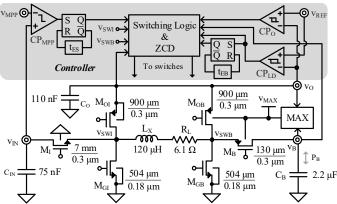

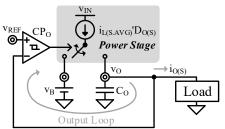

#### II. PROPOSED BATTERY-CHARGING VOLTAGE REGULATOR

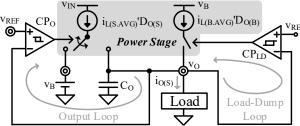

The proposed CMOS SLCR system is shown in Fig. 2. When the on-chip TEG's  $P_{MPP}$  exceeds the demand of the IoT load (i.e., sensor idles), this SLCR is in harvest mode. In harvest mode,  $M_I$  always closes, and  $M_{GB}$  closes to energize  $L_X$  from  $v_{IN}$ . Output hysteretic comparator  $CP_O$  dictates whether  $L_X$ 's energy is drained into output  $v_O$  or  $v_B$ . When  $v_O$  drops to  $CP_O$ 's lower hysteretic trip point  $v_{H(O)}$ ,  $CP_O$  trips low. Then, every time  $L_X$  drains, switching logic closes  $M_{OB}$  to supply  $v_O$ , so  $v_O$  rises. When  $v_O$  rises to  $CP_O$ 's upper hysteretic trip point  $v_{H(O^+)}$ ,  $CP_O$  trips high. Then, every time  $L_X$  drains, switching logic closes  $M_B$  to charge  $v_B$ . This way,  $CP_O$  limits  $v_O$  within its hysteretic window  $\Delta v_{H(O)}$  and charges  $v_B$  with excess available power.

Fig. 2. A CMOS switched-inductor charging regulator system.

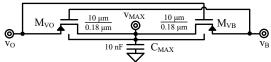

If the IoT load demands a power higher than  $P_{MPP}$ ,  $v_O$  will drop below  $v_{H(O-)}$ . When  $v_O$  hits the load-dump hysteretic comparator  $CP_{LD}$ 's lower trip point  $v_{H(LD-)}$ ,  $CP_{LD}$  trips low, and the SLCR enters battery-assist mode. In this mode,  $M_I$  always opens, and  $L_X$ ,  $M_B$ ,  $M_{GB}$ ,  $M_{GI}$ , and  $M_{OI}$  buck or boost  $v_B$  to  $v_O$ . The maximum voltage selector (the "MAX" block in Fig. 2) outputs the higher voltage between  $v_O$  and  $v_B$ , which is called  $v_{MAX}$ . Its schematic is shown in Fig. 3 [25]. When  $v_O$  is lower than  $v_B$ , switch  $M_{VB}$  closes to short  $v_B$  to  $v_{MAX}$ , and vice versa.

Fig. 3. Schematic of the maximum-supply selector.

SLCR is in discontinuous conduction mode (DCM) and adopts the constant-energy-packet scheme described in [25], which fixes the peak inductor current by fixing the energizing time under given  $v_{\rm IN}$ . The constant energy packet scheme keeps each energy packet the same and only adjusts the duration of energy delivery to adjust the power delivered (i.e., in Fig. 12 the harvester delivers energy for 260 ms each time with 20 nA load,

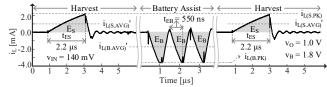

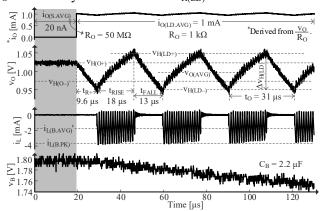

whereas it delivers energy for 830 ms each time with 40 nA load). Thus, its efficiency stays optimally flat across power level and is the same as the efficiency of each energy packet. Fixing the energizing time eliminates the need for an inner current loop. All energy packets  $E_{\rm S}$  drawn from  $v_{\rm IN}$  are identical in harvest mode (i.e., identical harvest-mode peak current  $i_{\rm L(S,PK)}$ , as in Fig. 4). In battery-assist mode, all energy packets that  $E_{\rm B}$  draws from  $v_{\rm B}$  are also identical (i.e., identical battery-assist mode peak current  $i_{\rm L(B,PK)}$ ).  $i_{\rm L}$  is negative in battery-assist mode because it reverses direction. In Fig. 4,  $i_{\rm L(S,AVG)}$ ' and  $i_{\rm L(B,AVG)}$ ' are the average  $i_{\rm L}$  across one  $E_{\rm S}$  and  $E_{\rm B}$ , respectively. Optimal  $i_{\rm L(S,PK)}$  and  $i_{\rm L(B,PK)}$  varies across  $v_{\rm IN}$  and  $v_{\rm O}$ , and the design of optimal packets is analyzed in detail in [25].

Fig. 4. Measured inductor current across operation modes.

If  $v_{IN}$  hits the TEG's maximum-power-Point (MPP) voltage  $v_{MPP}$  in harvest mode, MPP comparator  $CP_{MPP}$  trips, and the SLCR draws one  $E_S$  from  $v_{IN}$ .  $v_{IN}$  drops after drawing each  $E_S$  and recovers to  $v_{MPP}$  before drawing the next, as in Fig. 8. In battery-assist mode,  $E_S$  is intentionally skipped because supplying IoT load with enough power is a priority over harvesting energy from TEG. TEG outputs  $P_{MPP}$  if  $v_{IN}$  equals half  $v_S$ .  $v_{MPP}$  is chosen such that the average input voltage  $v_{IN(AVG)}$  equals half  $v_S$ .

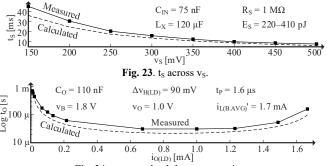

Delay t<sub>ES</sub> loops SR latch in Fig. 2 to generate energize time t<sub>ES</sub>. In harvest mode, L<sub>X</sub> energizes across t<sub>ES</sub> to harvest one E<sub>S</sub> from v<sub>IN</sub>, as in Fig. 4. t<sub>ES</sub> is optimized across v<sub>MPP</sub>, so the SLCR is optimally efficient across vs. Fig. 5 shows optimal i<sub>L(S.PK)</sub> across v<sub>S</sub>. With higher R<sub>S</sub>, the TEG avails less power, and the MOS switches' leakage loss signifies. Thus, the channel widths of MOS switches are narrow with higher R<sub>S</sub> to reduce leakage. This raises their conduction resistance and thus lowers the optimal peak current. The work does not need a current limit, as i<sub>L(PK)</sub> is at mA level. Loss analysis and measured efficiency of this proposed SLCR are in [25], and the max efficiencies in harvest and battery-assist mode are 77% and 88%, respectively. Delay t<sub>EB</sub> loops SR latch to generate energize time t<sub>EB</sub>. L<sub>X</sub> energizes across t<sub>EB</sub> in batteryassist mode to draw one E<sub>B</sub> from v<sub>B</sub>. t<sub>EB</sub> is optimized for nominal v<sub>B</sub> and v<sub>O</sub>, which are 1.8 V and 1 V, respectively.

Fig. 5. Optimally efficient  $i_{L(S.PK)}$  across  $v_s$ .

## A. Output Loop

Operation and Model:  $CP_O$ , output capacitor  $C_O$ , IoT load,  $v_B$ , and SLCR power stage close the output loop in harvest mode. Given the constant-energy-packet scheme, the output loop does not adjust  $i_{L(S.PK)}$  in harvest mode, as the  $i_L$  profile in Fig. 4 and 6 shows. Thus, although  $i_L$  varies at every time instance, the average  $i_L$  across one energy packet (labeled  $i_{L(S.AVG)}$  by

the dashed line in Fig. 4) is independent of the output loop. Given this independence, the SLCR power stage, on average, should be modeled as a current source in the output loop equivalent model in Fig. 7. This current source models the average current the SLCR outputs to  $v_O$  or  $v_B$ , which is a  $D_{O(S)}$  fraction of  $i_{L(S.AVG)}$ '.  $D_{O(S)}$  is  $M_{OB}$ 's or  $M_B$ 's duty cycle in harvest mode.  $i_{L(S.AVG)}$ ' nears half  $i_{L(S.PK)}$ . In harvest mode, the idling IoT load sources nA output current  $i_{O(S)}$ . The STDP switch is only a behavioral model that depicts  $CP_O$  directing energy to either  $v_O$  or  $v_B$ .

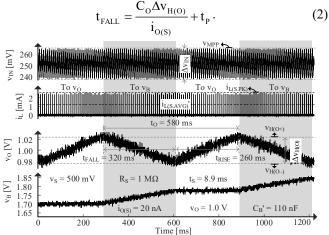

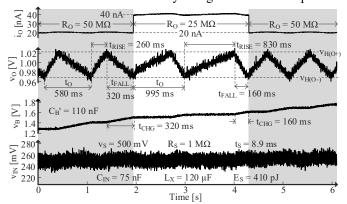

The model in Fig. 7 clearly shows that the output loop is fundamentally a relaxation oscillator. The current difference between  $i_{L(S.AVG)}$ ,  $D_{O(S)}$  and  $i_{O(S)}$  charges  $v_O$  when  $CP_O$  trips low, so  $v_O$  rises as its profile in Fig. 6 shows. Rise time  $t_{RISE}$  is

$$t_{RISE} = \frac{C_{o}\Delta v_{H(O)}}{i_{L(S,AVG)}'D_{O(S)} - i_{O(S)}} + t_{p},$$

(1)

where  $t_P$  is the comparator propagation delay. When  $v_O$  reaches  $v_{H(O^+)}$ ,  $CP_O$  trips high, and the oscillator "relaxes" to let  $i_{O(S)}$  drain  $v_O$ . Consequently,  $v_O$ 's fall time is

Fig. 6. Measured output loop large-signal oscillation waveforms.

When  $v_O$  hits  $v_{H(O-)}$ ,  $CP_O$  trips low, and the control logic demands that the SLCR charge  $v_O$  again. This marks the start of the next oscillation cycle. Thus,  $v_O$ 's oscillation period  $t_O$  is

$$t_{O} = t_{RISE} + t_{FALL}. (3)$$

$v_{IN}$  and  $i_L$  profiles in Fig. 6 show that  $v_{IN}$  drops by  $\Delta v_{IN}$ every time L<sub>X</sub> draws one E<sub>S</sub> from v<sub>IN</sub> and recovers thereafter. More importantly, Fig. 6 shows that the output loop does not adjust  $i_{L(S.PK)}$ , so  $i_{L(S.PK)}$  is independent of the output loop. Thus, Fig. 6 justifies the validity of modeling the SLCR power stage as a current source in the output loop model. v<sub>B</sub> charges up when vo falls, and Es packets reach v<sub>B</sub>. v<sub>B</sub> profile in Fig. 6 is measured using a small 110-nF storage capacitor C<sub>B</sub> for testing purposes only, to show discernable rise in v<sub>B</sub>. The system charges v<sub>B</sub> while keeping TEG at its MPP until v<sub>B</sub> hits the CMOS breakdown voltage, which is 1.8 V for this work. Afterward, the harvester only draws power from the TEG to supply P<sub>O</sub> without charging the v<sub>B</sub>. Thus, the TEG would deviate from its MPP. In this prototype, an off-chip FPGA monitors v<sub>B</sub>. Once v<sub>B</sub> hits V<sub>BD</sub>, the FPGA tells the SLCR to stop charging v<sub>B</sub>. Breakdown protection, as in [16], can be applied to this work as well.

Stability: An oscillation is stable and sustaining if the total phase shift and gain are 360° and 1 at the oscillation frequency  $f_0$  [26]. Negative feedback with an additional 180° phase shift at  $f_0$  provides a 360° phase shift. CP<sub>0</sub> reverses v<sub>0</sub>'s direction whenever it engages (trips). Because of this reversal effect, CP<sub>0</sub> closes a negative feedback loop and offers 180° phase shift  $\angle A_{CPO}$ .

Fig. 7. Output loop large-signal oscillator model.

$C_{\rm O}$  delays the rise and fall of  $v_{\rm O}$  and thus offers an additional phase shift at  $f_{\rm O}$ . After  $CP_{\rm O}$  engages and reverses  $v_{\rm O}$ 's direction when  $v_{\rm O}$  hits  $v_{\rm H(O-)}$  at 600 ms in Fig. 6,  $CP_{\rm O}$  "relaxes" and cannot keep engaging. This is because  $CP_{\rm O}$ 's trip point has risen from  $v_{\rm H(O-)}$  to  $v_{\rm H(O+)}$ , and  $C_{\rm O}$  delays the rise of  $v_{\rm O}$ .  $CP_{\rm O}$  re-engages and reverses  $v_{\rm O}$ 's direction at 900 ms after  $v_{\rm O}$  rising delay  $t_{\rm RISE}$ . After  $CP_{\rm O}$  re-engages at 900 ms, it "relaxes" again and cannot keep engaging. It engages again at 1200 ms after  $v_{\rm O}$ 's falling delay  $t_{\rm FALL}$ . Thus, the average delay  $t_{\rm DLY(AVG)}$  created by  $C_{\rm O}$  is the average of the rising and falling delays:

$$t_{\text{DLY(AVG)}} = \frac{t_{\text{RISE}} + t_{\text{FALL}}}{2} = \frac{t_{\text{O}}}{2}.$$

(4)

The effective phase shift  $\angle A_{DLY}$  caused by  $t_{DLY(AVG)}$  at  $f_O$  is

$$\angle A_{\text{DLY}}|_{f_0} = \left(\frac{t_{\text{DLY(AVG)}}}{t_0}\right) \times 360^\circ = 180^\circ \cdot$$

(5)

The output loop's total phase shift  $\angle A_{LG(O)}$  at  $f_O$  therefore is

$$\angle A_{LG(O)}|_{f_O} = \angle A_{CPO} + \angle A_{DLY}|_{f_O} = 360^{\circ} \cdot$$

(6)

$CP_O$ 's hysteretic window sets  $v_O$ 's oscillation amplitude and effectively forces the output loop's loop gain  $A_{LG(O)}$  to 1 at  $f_O$ :

$$\mathbf{A}_{\mathrm{LG(O)}}\big|_{\mathbf{f_0}} = 1 \, \cdot \tag{7}$$

Equations (6) and (7) justify that  $v_0$  oscillation is stable.

## B. MPP Loop

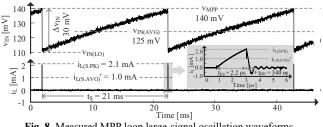

Operation and Model: On-chip TEG, input capacitor  $C_{IN}$ ,  $CP_{MPP}$ , SR latch and delay block  $t_{ES}$ , and SLCR power stage close the MPP loop. In harvest mode, if  $v_{IN}$  hits  $v_{MPP}$ , as in Fig. 8,  $CP_{MPP}$  trips high and triggers the SR latch in Fig. 2 to generate a pulse that closes  $M_{GB}$  to energize  $L_X$ . The fractional open-circuit voltage (FOCV) method [18] is applied to generate  $v_{MPP}$ . Pulse width is set by the  $v_{MPP}$ -dependent delay  $t_{ES}$ . Fig. 8 shows a zoomed-in  $i_L$  profile. For this particular  $E_S$ ,  $L_X$  drains to  $v_O$  across drain time  $t_{DO}$ .

The input voltage  $v_{\rm IN}$  rises every time after it plummets because the 250-mV source voltage  $v_{\rm S}$  charges the input capacitor  $C_{\rm IN}$  through the source resistance  $R_{\rm S}$ . The  $v_{\rm S}$  and  $R_{\rm S}$

are defined in Fig. 1. After v<sub>IN</sub> rises to v<sub>MPP</sub>, the MPP loop sends out an energizing command t<sub>ES</sub> so that the SLCR draws one energy packet from the source. Therefore, the input voltage  $v_{IN}$  drops. After drawing one energy packet,  $v_{IN}$  drops below v<sub>MPP</sub>, so CP<sub>MPP</sub> dictates the SLCR to stop drawing energy from the source. Therefore, the input voltage v<sub>IN</sub> can recover as v<sub>S</sub> charges C<sub>IN</sub> through R<sub>S</sub>. After a duration of t<sub>S</sub>, v<sub>IN</sub> recovers to v<sub>MPP</sub> again, and CP<sub>MPP</sub> trips to dictate the SLCR to draw the next energy packet. C<sub>IN</sub> suppresses the ripple of the  $v_{IN}$ , which is denoted as  $\Delta v_{IN}$  in Fig. 8. This way, the input voltage could be as close to a dc voltage as possible.

The optimal energizing time t<sub>ES</sub> that gives the highest efficiency is the result of balancing ohmic loss, charge loss, and leakage loss. The details of designing the optimal t<sub>ES</sub> are described in [25]. The 2.2-µs delay cell t<sub>ES</sub> loops the SR latch to generate this 2.2-µs energizing time pulse, which is ultimately triggered by the Maximum-Power-Point (MPP) comparator CP<sub>MPP</sub>. Once the input voltage v<sub>IN</sub> hits v<sub>MPP</sub> and causes CP<sub>MPP</sub> to trip, the output of the SR latch is set to high. After a delay of t<sub>ES</sub>, the reset signal of the SR latch trips high and then resets the output of the SR latch. As a result, a pulse of width t<sub>ES</sub> is generated.

Similarly, because of the constant-energy-packet scheme, the MPP loop does not adjust i<sub>L(S.PK)</sub>, as the i<sub>L</sub> profile in Fig. 8 shows. Thus, although i<sub>L</sub> varies at every time instance, the average i<sub>L</sub> across one energy packet (labeled as i<sub>L(S,AVG</sub>' by the dashed line in Fig. 4) is independent of the MPP loop. Therefore, the current source in Fig. 9 models the average current drawn by the SLCR from v<sub>IN</sub> across one E<sub>S</sub>, which is the i<sub>L(S.AVG</sub>' labeled in Fig. 4. This current source is enabled for a preset duration ( $t_{ES}$ ) every time  $CP_{MPP}$  trips high.

Fig. 8. Measured MPP loop large-signal oscillation waveforms.

The model in Fig. 9 shows that the MPP loop can also be interpreted as a relaxation oscillator. CP<sub>MPP</sub>'s trip point v<sub>MPP</sub> sets the upper bound of  $v_{\text{IN}}$ . Current source  $i_{\text{L(S.AVG}}$ ' discharges v<sub>IN</sub> from a designed C<sub>IN</sub> for a preset duration t<sub>ES</sub>. Thus, C<sub>IN</sub>,  $i_{L(S.AVG')}$ , and  $t_{ES}$  together set  $\Delta v_{IN}$ , which consequently sets  $v_{\rm IN}$ 's lower bound  $v_{\rm IN(LO)}$  as labelled in Fig. 8. Therefore, the MPP loop is also a hysteretic relaxation oscillator.

Fig. 9. MPP loop large-signal oscillation model

After drawing one E<sub>S</sub> from v<sub>IN</sub> at 2 ms, as Fig. 8 shows, source current is charges C<sub>IN</sub>, and therefore v<sub>IN</sub> rises. When v<sub>IN</sub> hits the hysteretic upper bound v<sub>MPP</sub> again, the SLCR draws one E<sub>S</sub> again and discharges v<sub>IN</sub> to the lower hysteretic bound v<sub>IN(LO)</sub> once more at 23 ms. This marks the start of the next oscillation cycle. The SLCR draws one E<sub>S</sub> per v<sub>IN</sub> oscillation period ts. To harvest the most power, the power drawn from  $v_{IN}$  should be close to  $P_{MPP}$ . Therefore,  $t_S$  is

$$t_{s} = \frac{E_{s}}{P_{s}} \approx \frac{E_{s}}{P_{MPP}} = \left(\frac{i_{L(S,PK)}^{2}}{2}\right) \left[\frac{R_{s}}{(0.5v_{s})^{2}}\right],$$

(8)

where the optimal  $i_{L(S,PK)}$  across  $v_S$  is shown in Fig. 5.

Stability: CP<sub>MPP</sub> reverses the direction of v<sub>IN</sub> every time it engages (discharges v<sub>IN</sub>). is always reverses v<sub>IN</sub>'s direction (charges v<sub>IN</sub>) after the SLCR draws one E<sub>S</sub>. Therefore, given this reversal effect, CP<sub>MPP</sub> and is establish negative feedback. C<sub>IN</sub> delays the rising of v<sub>IN</sub> as i<sub>S</sub> requires about 21 ms to charge v<sub>IN</sub> as Fig. 8 shows. C<sub>IN</sub> also delays the falling of v<sub>IN</sub> because it takes the SLCR one t<sub>ES</sub> to discharge C<sub>IN</sub>. Thus, for reasons similar to those stated for the output loop, C<sub>IN</sub> also adds a 180° phase shift at v<sub>IN</sub>'s oscillation frequency f<sub>S</sub>.  $i_{L(S.AVG)}$ ,  $t_{ES}$ , and  $C_{IN}$  set  $v_{IN}$ 's oscillation amplitude  $\Delta v_{IN}$ . Thus, the MPP loop's gain is 1 at f<sub>s</sub>. Therefore, for the same reasons stated for the output loop, the MPP loop oscillation is also stable.

### C. Load-Dump Loop

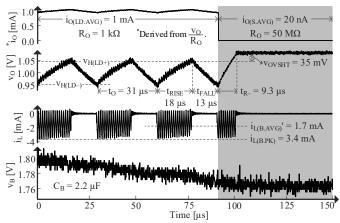

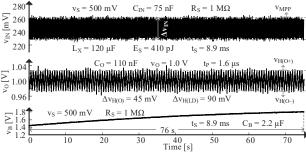

Operation and Model: The CPLD, Co, IoT load, and SLCR power stage close the load-dump loop. When the IoT load draws high load-dump current  $i_{O(LD)}$ ,  $v_O$  drops to  $v_{H(LD-)}$  at 27 μs, as in Fig. 10. Then, CP<sub>LD</sub> trips low, and the SLCR enters battery-assist mode to deliver consecutive E<sub>B</sub> packets to v<sub>O</sub>. When CP<sub>LD</sub> trips low, CP<sub>LD</sub> is designed to override CP<sub>O</sub> to prevent racing between the output loop and the load-dump loop. When v<sub>O</sub> hits v<sub>H(LD+)</sub>, CP<sub>LD</sub> trips high, and the SLCR stops drawing E<sub>B</sub> from v<sub>B</sub>, so v<sub>O</sub> falls. This way, CP<sub>LD</sub> limits  $v_0$  within its hysteretic window  $\Delta v_{H(LD)}$ .

Fig. 10. Measured positive load dump transient waveforms.

Given the constant-energy-packet scheme, the load-dump loop does not adjust i<sub>L(B.PK)</sub> and E<sub>B</sub> as in Fig. 10. Thus, during t<sub>RISE</sub>, the average current the SLCR delivers to v<sub>O</sub> is independent of the load-dump loop. Thus, although i<sub>L</sub> varies at every time instance, the average it across one energy packet (labeled as i<sub>L(B,AVG</sub>' by the dashed line in Fig. 4) is independent of the output loop. Similarly, because of this independency, the SLCR power stage is also modeled as a current source in the load-dump loop equivalent model in Fig. 11. During  $t_{RISE}$ , the load-dump loop current source is enabled, and the current that the SLCR outputs from  $v_B$  to  $v_O$  is a  $D_{O(B)}$  fraction of  $i_{L(B.AVG)}$ , where  $i_{L(B.AVG)}$  is the average  $i_L$  across one  $E_B$  packet, as the  $i_L$  profiles show in Fig. 4 and 10, which is half  $i_{L(B.PK)}$ .  $D_{O(B)}$  is the SLCR's output duty cycle. It is 1 if the SLCR bucks  $v_B$  to  $v_O$ ; and  $D_{O(B)}$  is  $M_{OI}$ 's duty cycle if the SLCR boosts  $v_B$  to  $v_O$ .

The model in Fig. 11 shows that the load-dump loop is also fundamentally a relaxation oscillator. The current difference between  $i_{L(B.AVG)}$ ,  $'D_{O(B)}$  and  $i_{O(LD)}$  charges  $v_O$  when  $CP_{LD}$  trips low, so  $v_O$  rises, as in Fig. 10. $v_O$ 's rise time  $t_{RISE}$  is

$$t_{\text{RISE}} = \frac{C_{\text{O}} \Delta v_{\text{H(LD)}}}{i_{\text{L(B.AVG)}} D_{\text{O(B)}} - i_{\text{O(LD)}}} + t_{\text{p}},$$

(9)

where  $t_P$  is  $CP_{LD}$ 's propagation delay. When  $v_O$  hits  $v_{H(LD^+)}$ ,  $CP_{LD}$  trips high, and the SLCR stops delivering  $E_B$  packets, so  $i_{O(LD)}$  drains  $v_O$ . Fall time  $t_{FALL}$  is

$$t_{\text{FALL}} = \frac{C_{\text{O}} \Delta v_{\text{H(LD)}}}{i_{\text{O(LD)}}} + t_{\text{P}} . \tag{10}$$

When  $v_O$  falls to  $v_{H(LD-)}$ ,  $CP_{LD}$  trips low, and SLCR draws  $E_B$  to charge  $v_O$  again, which marks the start of the next oscillation cycle. The load-dump loop's  $t_O$  is the same as in (3).

Fig. 11. Load-dump loop large-signal oscillator model.

<u>Stability</u>: The load-dump loop, if alone, is stable for reasons similar to those stated for the output loop. However, the load-dump loop is not alone, as the output loop parallels it. Fig. 11 shows this parallel arrangement. If  $v_{IN}$  hits  $v_{MPP}$  when a falling  $v_O$  falls between  $v_{H(O-)}$  and  $v_{H(LD-)}$ , the output loop tries to deliver one  $E_S$  to  $v_O$ . However, because  $P_{MPP}$  is too low to supply  $P_O$  when the load current is high,  $v_O$  keeps falling and would inevitably drop below  $v_{H(LD-)}$ . This means the output loop is railed out so that  $v_O$  keeps dropping despite the output loop's actions. Because it has been railed out, the output loop's gain  $A_{LG(O)}$  is effectively zero:

$$A_{LG(O)}\Big|_{RAHED-OUT} = 0.$$

(11)

When the load-dump loop relaxes as  $v_{\rm O}$  falls, it leaves only a railed-out output loop with zero loop gain. Thus, the load-dump loop dominates the output loop in battery-assist mode, and no instability would arise from paralleling two loops.

#### D. Response Time

<u>Light Load Dump</u>: If  $P_{MPP}$  can supply the variation of  $P_O$ , the SLCR stays in harvest mode, and this paper calls this light  $P_O$  variation a "light load dump." Fig. 12 shows measured responses of rising and falling light load dumps when  $i_{O(S)}$  steps

between 20 nA and 40 nA. A higher  $i_O$  demands more  $E_S$  to charge  $v_O$  from  $v_{H(O^+)}$  to  $v_{H(O^+)}$ , so  $t_{RISE}$  increases from 260 ms to 830 ms.  $t_{FALL}$  decreases from 320 ms to 160 ms because a higher  $i_{O(S)}$  discharges  $v_O$  faster. Because less  $E_S$  reaches  $v_B$  with a higher  $i_{O(S)}$ ,  $v_B$  charges with shorter charging interval  $t_{CHG}$ , as the  $v_B$  profile shows. Because the SLCR needs not activate the load-dump loop for light load dumps, it responds within one  $t_O$ .

<u>Heavy Load Dump</u>: If  $P_{MPP}$  is insufficient to supply the increase of  $P_O$ , the SLCR must activate the load-dump loop and enter battery-assist mode. Similarly, if there is a drastically falling load dump, the SLCR must deactivate the load-dump loop and re-enter harvest mode. This paper calls this drastic  $P_O$  variation a "heavy load dump." Fig. 10 shows measured waveforms of a heavy rising 1-mA load dump.

Fig. 12. Transient waveforms of a light load dump.

Confronting a heavy rising load dump when  $v_O$  is nearing  $v_{H(O^+)}$  results in the worst-case response time  $t_{R^+}$ . As Fig. 10 shows,  $v_O$  is nearing  $v_{H(O^+)}$  when  $i_O$  steps from 20 nA to 1 mA at 20  $\mu$ s. To activate the load-dump loop,  $v_O$  must fall from  $v_{H(O^+)}$  to  $v_{H(D^-)}$ . This means  $i_{O(LD)}$  must discharge  $v_O$  across the widest voltage range, which is the most time-consuming and results in the worst-case  $t_{R^+}$ . In Fig. 10,  $v_O$  hits  $v_{H(LD^-)}$  at about 29  $\mu$ s, and the measured  $t_{R^+}$  is about 9.6  $\mu$ s. Worst-case  $t_{R^+}$  is  $v_O$ 's worst-case discharge time plus  $CP_{HYS}$ 's  $t_P$ , as in (12).

$$t_{R+} = \frac{C_{O} \left(0.5\Delta v_{H(O)} + 0.5\Delta v_{H(LD)}\right)}{i_{O(ID)}} + t_{P}.$$

(12)

Confronting a heavy falling load dump when  $v_O$  is nearing  $v_{H(LD-)}$  results in worst-case response time  $t_{R-}$ . Fig. 13 shows measured waveforms under a heavy falling 1-mA load dump. When  $v_O$  is nearing  $v_{H(LD-)}$  at 90  $\mu$ s,  $i_O$  steps from 1 mA to 20 nA. To de-activate the load-dump loop and exit battery-assist mode,  $v_O$  must reach  $v_{H(LD+)}$  from  $v_{H(LD-)}$ . This means the SLCR must charge  $v_O$  across the widest voltage range, which is the most time-consuming and results in the worst-case  $t_{R-}$  CP<sub>LD</sub> reacts a  $t_P$  after  $v_O$  hitting  $v_{H(LD+)}$ , and therefore causes an overshoot. Measured overshoot voltage  $v_{OVSHT}$  is 35 mV with 1.6- $\mu$ s  $t_P$ , and the resulting  $t_{R-}$  is 9.3  $\mu$ s. Worst-case  $t_{R-}$  is  $v_O$ 's worst-case charging time plus CP<sub>HYS</sub>'s  $t_P$ , as in (13).

$$t_{R_{-}} = \frac{C_{o} \Delta v_{\rm H(LD)}}{i_{\rm L(B.AVG)} \, 'D_{\rm O(B)} - i_{\rm O(S)}} + t_{\rm p} \approx \frac{C_{o} \Delta v_{\rm H(LD)}}{i_{\rm L(B.AVG)} \, 'D_{\rm O(B)}} + t_{\rm p} \cdot (13)$$

Fig. 13. Measured negative load dump transient waveforms.

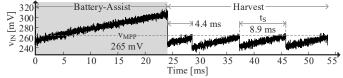

Because the switching logic skips  $E_{\rm S}$  packets in battery-assist mode,  $v_{\rm IN}$  may reach beyond  $v_{\rm MPP}$ . After a falling heavy load dump, the MPP loop and  $v_{\rm IN}$  must resettle to steady state. As Fig. 14 shows, when the SLCR exits battery-assist mode at 23.5 ms, the MPP loop immediately draws consecutive  $E_{\rm S}$  packets from  $v_{\rm IN}$  until  $v_{\rm IN}$  drops below  $v_{\rm MPP}$ . Because  $v_{\rm IN}$ 's valley value at 23.5 ms is higher than  $v_{\rm IN}$ 's steady state valley value, it takes  $v_{\rm IN}$  only 4.4 ms (less than steady state  $t_{\rm S}$ , which is 8.9 ms) to recharge to  $v_{\rm MPP}$  again. Thus,  $v_{\rm IN}$  hits  $v_{\rm MPP}$  again at 28 ms, and MPP loop draws another  $E_{\rm S}$ . After 28 ms, the MPP loop settles to steady state. As a result, the MPP loop settles within one  $t_{\rm S}$ .

Fig. 14. Measured  $v_{\text{IN}}$  recovery during a negative load dump.

### III. PROTOTYPE DESIGN

#### A. IoT Wireless Microsensor

To reduce power consumption, IoT wireless microsensors mostly idle and sense and transmit data only on demand. Fig. 15 shows the load current profile of a typical IoT wireless microsensor. When idling, state-of-the-art (SoA) sensors may consume sub-nW standby power [27]. Some sensors adopt always-on wake-up receivers (Rx), and SoA wake-up Rx may consume sub-nW [28], leading to sub-nW total standby power. Thus, idle load current io(IDLE) in Fig. 15 is sub-nW.

Fig. 15. Typical load profile of IoT wireless microsensors.

When sensing, SoA sensors consume  $10{\text -}100$  nW [1, 25], so the sensing load current  $i_{\text{O(SNS)}}$  is on the order of nA. During transmission, SoA transmitters (Tx) may consume 1.2 mW from  $0.8{\text -}1.0$  V supply voltages [12]; thus, transmission load current  $i_{\text{O(XFER)}}$  is on the order of 1 mA. The duration of each transmission ( $t_{\text{XFER}}$ ) is 500  $\mu$ s-7 ms [13-14]. Practical IoT sensors may transmit only four times per day [15], so

idling time  $t_{IDLE}$  is much longer than sensing time  $t_{SNS}$  and  $t_{XFER}$ . As a result, average load current  $i_{O(AVG)}$  is nearing  $i_{O(IDLE)}$ . Table II lists typical performances of SoA IoT wireless microsensors.

TABLE II: SOA LOW-POWER IOT WIRELESS MICROSENSORS

| Item                 | Value      | Item                | Value     | Item                 | Value       |  |

|----------------------|------------|---------------------|-----------|----------------------|-------------|--|

| $v_{o}$              | 0.8-1.0 V  | $t_{XFER}$          | 0.5–7 ms  | _                    | -           |  |

| P <sub>O(IDLE)</sub> | 410–810 pW | $P_{O(SNS)}$        | 6.4–43 nW | P <sub>O(XFER)</sub> | 0.63-1.2 mW |  |

| i <sub>O(IDLE)</sub> | 410-810 pA | i <sub>O(SNS)</sub> | 6.4-43 nA | i <sub>O(XFER)</sub> | 0.63-1.2 mA |  |

## B. Hystereses

$\Delta v_{H(O)}$  and  $\Delta v_{H(LD)}$  must overcome noise floor  $v_N^*$  so that  $CP_O$  and  $CP_{LD}$  can trip properly. Therefore,  $CP_O$ 's hysteretic window  $\Delta v_{H(O)}$  should be much greater than  $v_N^*$ , as in (14).

$$\Delta v_{H(O)} >> v_N^* \cdot \tag{14}$$

$CP_{LD}$ 's hysteretic window  $\Delta v_{H(LD)}$  must be amply separated from  $\Delta v_{H(O)}$  so that  $CP_{LD}$  does not misfire in the presence of noise, as in Fig. 10. Thus,  $\Delta v_{H(LD)}$  'ss design constraints is

$$\Delta v_{H(LD)} - \Delta v_{H(O)} >> v_N^* . \tag{15}$$

#### C. Input Capacitor

$C_{IN}$  suppresses  $\Delta v_{IN}$ . When drawing  $E_S$  from  $v_{IN}$ ,  $C_{IN}$  supplies energy  $\Delta E_{CIN}$  temporarily, and  $v_{IN}$  drops from  $v_{MPP}$  to  $(v_{MPP}-\Delta v_{IN})$ . Because  $R_S$  is on the order of  $M\Omega$ ,  $C_{IN}$  temporarily supplies most  $E_S$  energy, so  $E_S$  is roughly  $\Delta E_{CIN}$ , as in (16).

$$E_{L} \approx \Delta E_{CIN} = 0.5 C_{IN} \left[ v_{MPP}^{2} - \left( v_{MPP} - \Delta v_{IN} \right)^{2} \right]. \tag{16}$$

Therefore,  $\Delta v_{IN}$  is

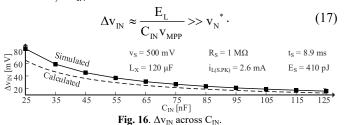

However,  $\Delta v_{IN}$  must be large enough to overcome  $v_N^*$  so  $CP_{MPP}$  can trip properly, as (17) depicts. Fig. 16 shows calculated and simulated  $\Delta v_{IN}$  across  $C_{IN}$ . This work sets  $\Delta v_{IN}$  to 30 mV to overcome  $v_N^*$ , and the resulting  $C_{IN}$  is 75 nF.

### D. Output Capacitor

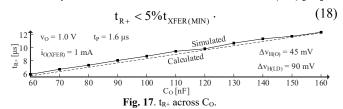

$t_R$  dictates  $C_O$  selection. This design aims at fast response against rising heavy load dumps.  $t_{R^+}$  is set to be less than 5% of the 500-µs minimum transmission duration  $t_{XFER(MIN)}$  [13]:

For a Tx that draws 1-mA  $i_{O(XFER)}$  from 1-V  $v_O$ , forcing (12) less than 5%  $t_{XFER(MIN)}$  results in (19), which demands  $C_O$  < 350 nF. Fig. 17 shows simulated and calculated  $t_{R+}$  across  $C_O$ . For design margin, this work uses a 110-nF  $C_O$ .

$$C_{O} < \frac{\left(5\%t_{XFER(MIN)} - t_{P}\right)i_{O(XFER)}}{0.5\Delta v_{H(O)} + 0.5\Delta v_{H(LD)}}.$$

(19)

## E. Storage Capacitor

When the ambient energy source disappears, IoT sensors become offline. IoT sensors must transmit all data previously acquired, in addition to sending an off-line report [29]. Each transmission event requires energy  $E_{XFER}$ :

$$E_{XFER} = P_{O(XFER)} t_{XFER} . (20)$$

Therefore, storage capacitor  $C_B$  must hold enough energy to sustain two  $E_{XFER}$ . To minimize the size of  $C_B$ ,  $C_B$  must hold the highest energy with lowest capacitance. This means  $v_B$  should start at its maximum voltage, which is the CMOS breakdown voltage  $V_{BD}$ . Assuming two  $E_{XFER}$  discharge  $C_B$  by  $\Delta v_B$ , the energy  $\Delta E_{CB}$  drawn from  $C_B$  is

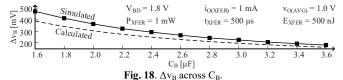

$$\Delta E_{CB} = 0.5 C_B \left[ V_{BD}^2 - \left( V_{BD} - \Delta v_B \right)^2 \right] \approx 2 E_{XFER} \,. \tag{21}$$

Therefore,  $\Delta v_B$  is

$$\Delta v_{\rm B} = V_{\rm BD} - \sqrt{V_{\rm BD}^2 - \frac{2E_{\rm XFER}}{0.5C_{\rm B}}} \ . \tag{22}$$

Simulated and calculated  $\Delta v_B$  across  $C_B$  are illustrated in Fig. 18. To prevent crashing  $v_B$ , this design chooses a 2.2- $\mu$ F  $C_B$ , and the resulting  $\Delta v_B$  is about 400 mV. SPICE simulation generated the simulation results shown in Fig. 16–18.

#### IV. MEASURED PERFORMANCE

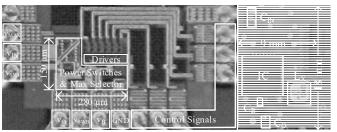

The 180-nm CMOS prototype in Fig. 19 integrates the power switches, gate drivers, and max block (Fig. 2). The printed circuit board (PCB) shows the  $5 \times 5$  mm<sup>2</sup> IC package and the  $3 \times 3 \times 1$  mm<sup>3</sup> inductor.  $C_{IN}$ ,  $C_{O}$ , and  $C_{B}$  are multi-layer ceramic capacitors. Their total leakage loss, measured by Keithley 6485 Pico-Ammeter with  $\pm 10$ -fA accuracy, is 60–70 pW. Like [25, 30], an onboard voltage source emulates onchip TEG's v<sub>S</sub>, and a 1-MΩ onboard resistor emulates R<sub>S</sub>. A field-programmable gate array (FPGA) controls the SLCR. State-of-the-art on-chip controllers consume around 50 pJ / cycle, as in [25]. In harvest mode, this translates to a current consumption of 1.25–5 nA, given t<sub>S</sub> is around 10–40 ms, as in Fig. 23, and the controller supply  $v_{MAX}$  could be as low as 1 V. The impact of the controller power consumption is presented in detail in [25] and shows that the controller power would decrease the overall efficiency by 8%.

A grounded metal noise shield encloses the PCB and reduces noise at low power level for all measurements. Additionally, all measurements were conducted in a noise-shielded metal chamber. Onboard off-the-shelf unity-gain buffers with 2-fA input current drives all voltage probes to prevent them from loading the Device Under Test (DUT) directly.

Fig. 19. 180-nm CMOS die and PCB photograph.

## A. Response Time

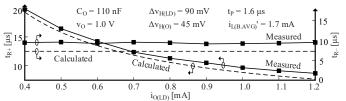

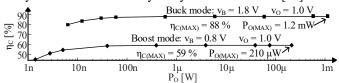

Measured and calculated  $t_{R^+}$  and  $t_{R^-}$  across load dump current  $i_{O(LD)}$  are shown in Fig. 20. For increasing  $i_{O(LD)}$ ,  $t_{R^+}$  shortens because  $i_{O(LD)}$  discharges  $v_O$  faster from  $v_{H(O^+)}$  to  $v_{H(LD^-)}$ . For falling heavy load dumps, pre-determined constant  $E_B$  packets charge  $C_O$  from  $v_{H(LD^-)}$  to  $v_{H(LD^+)}$ . Constant  $E_B$  packets are independent of  $i_{O(LD)}$ ; therefore,  $t_{R^-}$  is approximately independent of  $i_{O(LD)}$ . Assuming a  $i_{O(XFER)}$  of about 1 mA, as Section III. A. justifies,  $t_{R^+}$  is 9.6  $\mu$ s when the IoT sensor abruptly activates data transmission.

Fig. 20.  $t_{R\pm}$  across load-dump current  $i_{O(LD)}$ .

### B. Accuracy

<u>Static</u>: When the SLCR reaches steady state in harvest mode,  $v_O$  ripples within  $\Delta v_{H(O)}$ . Because millisecond  $t_O$  is much greater than microsecond  $t_P$  in harvest mode,  $t_P$ 's effect on static  $v_O$  error  $v_{OE(S)}$  is negligible. Therefore,  $v_{OE(S)}$  is approximately half the hysteretic window  $\Delta v_{H(O)}$  as in (23).

$$v_{OE(S)} = \pm \left[ 0.5 \Delta v_{H(O)} + t_{P} \left( \frac{dv_{O}}{dt} \right) \right] \approx \pm 0.5 \Delta v_{H(O)}.$$

(23)

<u>Dynamic</u>: Dynamic  $v_O$  error  $v_{OE(D)}$  gauges  $v_O$  accuracy under rising and falling heavy load dumps. Because  $t_P$  is comparable to  $t_{R^+}$  and  $t_{R^-}$ ,  $t_P$ 's effects on  $v_{OE(D)}$  are noticeable.  $t_P$  exacerbates dynamic  $v_O$  error  $v_{OE(D)^+}$  under rising heavy load dumps because  $i_{O(LD)}$  keeps discharging  $v_O$  below  $v_{H(LD^-)}$  before  $CP_{LD}$  can react. Therefore,  $v_{OE(D)^+}$  is half  $\Delta v_{H(LD)}$  plus the extra drop caused by  $t_P$  as in (24).

$$v_{OE(D)+} = 0.5\Delta v_{H(LD)} + t_{P} \left(\frac{i_{O(LD)}}{C_{O}}\right).$$

(24)

$t_P$  exacerbates dynamic  $v_O$  error  $v_{OE(D)-}$  under falling heavy load dumps as extra  $E_B$  would overcharge  $v_O$  beyond  $v_{H(LD+)}$  before  $CP_{LD}$  can tell the SLCR to stop delivering  $E_B$  packets.  $v_{OE(D)-}$  is half  $\Delta v_{H(LD)}$  plus the extra overcharge caused by  $t_P$ :

$$v_{OE(D)^{-}} \approx 0.5 \Delta v_{H(LD)} + t_{p} \left( \frac{i_{L(B.AVG)}' D_{O(B)}}{C_{O}} \right).$$

(25)

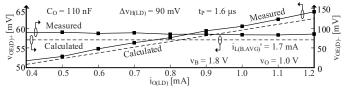

Measured and calculated  $v_{OE(D)^+}$  and  $v_{OE(D)_-}$  are shown in Fig. 21. As  $i_{O(LD)}$  increases,  $v_O$  drops faster under falling heavy load dumps. Therefore  $v_{OE(D)^+}$  increases because with higher

$i_{O(LD)}$ ,  $v_O$  would drop lower during a given  $t_P$ . Like  $t_{R-}$ ,  $v_{OE(D)-}$  is roughly independent from  $i_{O(LD)}$  because the pre-determined constant  $E_B$  packets overcharge  $v_O$ .

Fig. 21. Dynamic output error.

#### C. Oscillation Periods

<u>Output Loop</u>: Measured and calculated harvest-mode  $t_O$  across static load current  $i_{O(S)}$  is shown in Fig. 22. As  $i_{O(S)}$  increases,  $t_{FALL}$  shortens with increasing  $i_{O(S)}$  because a higher  $i_{O(S)}$  discharges  $v_O$  faster. Therefore,  $t_O$  shortens at first because  $t_{FALL}$  decreases. As  $i_{O(S)}$  keeps increasing, charging  $v_O$  from  $v_{H(O-)}$  to  $v_{H(O+)}$  requires more  $E_S$ . Therefore,  $t_{RISE}$  increases with increasing  $i_{O(S)}$ , and  $t_O$  eventually starts to increase as  $i_{O(S)}$  increases. The measured shortest  $t_O$  is about 580 ms, so the maximum harvest-mode oscillating frequency  $f_O$  is 1.7 Hz. As  $v_S$  rises, the TEG avails more power so the SL charges the output faster as each energy packet becomes larger (i.e., higher  $i_{L(PK)}$  as Fig. 5 shows). Thus,  $t_{RISE}$  decreases as  $v_S$  rises. Comparators execute system operation without a clock. So, the system automatically adjusts its frequency according to  $R_S$  and can offset non-idealities such as  $R_S$  variation.

Fig. 22. to across static load current i<sub>O(S)</sub>.

<u>MPP Loop</u>: Measured and calculated  $t_S$  across  $v_S$  are shown in Fig. 23. The energy source avails more power as  $v_S$  rises. Therefore, the MPP loop draws more frequent  $E_S$  packets from  $v_{IN}$  so  $t_S$  drops. Calculated  $t_S$  deviates more from measured  $t_S$  when  $v_S$  is low. This is because with lower  $v_S$ ,  $\Delta v_{IN}$  becomes comparatively more significant, while (8) neglects  $\Delta v_{IN}$ . As  $\Delta v_{IN}$  becomes more significant, the power drawn by the SLCR becomes less and less than  $P_{MPP}$ . Therefore, calculated  $t_S$  deviates more from measured  $t_S$  as  $v_S$  decreases.

Fig. 24. t<sub>O</sub> across load-dump current i<sub>O(LD)</sub>.

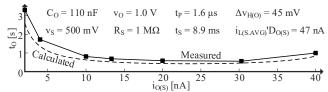

<u>Load Dump Loop</u>: Measured and calculated load-dump loop to across load dump current io<sub>(LD)</sub> is shown in Fig. 24.

Similarly, there exists a minimum for the  $t_0$  of the load-dump loop. The measured shortest load-dump loop  $t_0$  is about 31  $\mu$ s, so the maximum load-dump loop  $f_0$  is about 32 kHz.

## D. Charging Profile

Fig. 25 measures the charging profile across 76 seconds to let  $v_B$  charge to  $V_{BD}$ .  $CP_O$ 's hysteretic window sustains and bounds  $v_O$ 's oscillation.  $v_{IN}$  is about 0.5  $v_S$  with 30-mV  $\Delta v_{IN}$ .

Fig. 25. Charging profile.

# E. Efficiency

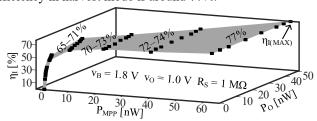

Fig. 26 measures the efficiency of the fast energy-harvesting SLCR prototype in harvest mode [25]. The harvest-mode efficiency  $\eta_I$  stays flat at the optimal level across load power  $P_O$  as mentioned in Section II, thanks to the constant energy packet scheme.  $\eta_I$  decreases as the maximum available power  $P_{MPP}$  decreases, given that the leakage loss of the MOSFET switches does not scale with  $P_{MPP}$ . As  $P_{MPP}$  decreases, leakage loss becomes more dominant, and thus  $\eta_I$  plummets. The peak efficiency in harvest mode is around 77%.

Fig. 26. Measured harvest-mode efficiency across  $P_{\text{MPP}}$  and  $P_{\text{O}}$ .

Fig. 27 measures the efficiency of the fast energy-harvesting SLCR prototype in battery-assist mode [25]. Similarly, because of the constant energy packet scheme, the battery-assist mode efficiency  $\eta_C$  stays flat at the optimal level across load power  $P_0$  as well. As load power  $P_0$  scales down, the leakage loss of the MOSFET switches (which does not scale with  $P_0$ ) similarly starts to dominate, so  $\eta_C$  drops. The peak efficiency in battery-assist mode is around 88% when bucking and around 59% when boosting. Switch  $M_B$ 's conduction resistance rises as  $v_B$  lowers, therefore the efficiency in boost mode is lower than that in buck mode. This paper focuses on control loop analysis but not on efficiency analysis. Detailed efficiency analysis is available in [25].

Fig. 27. Measured battery-assist mode efficiency across Po.

### F. Relative Performance

Table III compares SoA CMOS SLCRs. The design in [17] is an energy-harvesting charger that incorporates a low dropout (LDO) regulator to supply the 1.2-V load. Its fundamental drawback is that if  $v_B$  is lower than  $v_O$ , the design in [17] cannot supply the load.

The designs in [21–24] report 100  $\mu$ s–2.5 ms  $t_R$ . The design in [21] uses a clocked pulse frequency modulation (PFM) scheme, which adjusts switching frequency f<sub>SW</sub> according to the load demand. But the design in [21] must wait two clock cycles before it increases fsw to react to load dumps, which leads to a slow 2.5 ms t<sub>R+</sub> under a 180 μA rising load dump. 2.5 ms  $t_{R+}$  is too slow given that  $t_{XFER}$  is 500  $\mu$ s-7 ms. Similarly, in [22], the converter must wait until the clock's falling edge before it reacts to rising load dumps. So, the resulting  $t_{R+}$  is still 100 µs. Designs in [23–24] use voltage mode pulse width modulation (PWM) in battery-assist mode. These designs need 2.2- or 10-µF Co to establish a lowfrequency dominant pole to stabilize the voltage loop. The drawback is that a higher Co results in a longer time for vo to discharge below  $v_{H(LD-)}$  (or charge beyond  $v_{H(LD+)}$ ). Consequently,  $t_R$  is 100  $\mu$ s to 2.5 ms.

Thanks to the proposed self-oscillating nested hysteretic control, capacitor selection does not affect loop stability, as Section II justifies. Therefore, the  $C_{\rm IN}$ ,  $C_{\rm O}$ , and  $C_{\rm B}$  selected for this design are 1.3–1300×, 9.1–91×, and 45× smaller than the SoA. This not only reduces system size but also accelerates loop response. The measured response time is 9.6  $\mu$ s, which is 10–260× faster than the SoA. Although this proposed system creates large and frequency-varying output voltage ripples, the frequencies of such ripples are no higher than 32 kHz in battery-assist mode and 1.7 Hz in harvest mode. An LDO usually provides good power supply rejection (PSR) up to 100 kHz bandwidth and can be added to suppress the output voltage ripple if necessary. This specific implementation excludes a cold-start feature, but a cold-start sequence similar to [30] is applicable to this work. It uses a starter circuit to

build up high voltage on a small capacitor from which it bootstraps the SL afterwards. With this control, power supplies can respond faster to IoT sensor's power demands.

#### V. CONCLUSIONS

This paper proposes a fast self-oscillating nested hysteretic CMOS switched-inductor charging regulator microsystem that harvest energy from resistive on-chip thermoelectric generators to power IoT sensors. The principle is to analyse the proposed hysteretic control as relaxation oscillators. This paper contributes detailed theory and insightful expressions on hysteretic loop stability, oscillation period, response time, and accuracy. This paper also contributes intuitive expressions that guide system level design (i.e., input, output, and storage capacitors, and hysteretic windows). A 180-nm CMOS prototype validates the proposed control. The measured response time is 9.6  $\mu$ s, which is  $10-260\times$  faster than prior arts.

#### ACKNOWLEDGMENT

The authors thank Drs. A. Blanco, O. Lazaro, N. Xing, J. Morroni, and Texas Instruments for their sponsorship.

#### REFERENCES

- [1] H. Wang *et al.*, "A battery-powered wireless ion sensing system consuming 5.5 nW of average power," in *IEEE J. Solid-State Circuits*, vol. 53, no. 7, pp. 2043–2053, July 2018.

- [2] T. Chang and G. A. Rincón-Mora, "Lowest v<sub>IN</sub> possible for switched-inductor boost converters," in *IEEE Midwest Symp. on Circuits and Syst.*, Dallas, TX, 2019.

- [3] Hi-Z Inc., HZ-2 thermoelectric generator module.

- [4] Hi-Z Inc., HZ-14 thermoelectric generator module.

- [5] Hi-Z Inc., HZ-14HV thermoelectric generator module.

- [6] TECTEG MFR., TEG1-PB-12611-6.0 thermoelectric generator module.

- [7] M. H. Ghaed et al., "Circuits for a cubic-millimeter energy-autonomous wireless intraocular pressure monitor," in *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 60, no. 12, pp. 3152–3162, Dec. 2013.

- [8] X. Yu et al., "Thermal matching designed CMOS MEMS-based thermo electric generator for naturally cooling condition," in Symposium on Design,

TARLE III. RELATIVE PERFORMANCE

| Parameter                  | [21]        | [22]    | [16]      | [17]           | [18]      | [19]              | [20]             | [23]  | [24]  | This work |

|----------------------------|-------------|---------|-----------|----------------|-----------|-------------------|------------------|-------|-------|-----------|

| Tech. [nm]                 | 180         | 500     | 180       | 180            | 28        | 180               | 180              | 180   | 210   | 180       |

| $v_{S}[V]$                 | -           | -       | 1         | 0.05-1         | 0.2-0.8** | 0.06-0.18**       | $0.1 – 0.6^{**}$ | -     | _     | 0.15-0.5  |

| $R_{S}[M\Omega]$           | _           | -       | _         | 0.16           | 0.00053   | 0.00021           | ı                | _     | _     | 1.0       |

| v <sub>o</sub> [V]         | 1.0 and 1.8 | 1.0-3.3 | 1.0       | 1.2 V from LDO | 0.4-1.4   | 1.0, 1.3, and 1.6 | 0.5 and 1.2      | 1.0   | 1.0   | 1.0       |

| i <sub>O</sub> [mA]        | -           | -       | 10-5-10-3 | < 2            | 0.001-60  | -                 | 0.01-2.5         | 0-1.0 | 0-10  | 0-1.6     |

| $v_B[V]$                   | 3.0         | -       | 2.9-4.1   | 1.3            | 1.8       | 2.4               | 1.2              | 1.8   | 1.8   | 1.8       |

| C <sub>IN</sub> [nF]       | 10000       | 4700    | _         | 10000          | -         | 10000             | 10000            | 220   | 100   | 75        |

| C <sub>O</sub> [nF]        | 10000       | 10000   | _         | 10000          | 1000      | 2200              | 1000             | 2200  | 10000 | 110       |

| $C_B[nF]$                  | _           | -       | _         | 100            | -         | _                 | 100              | -     | _     | 2.2       |

| $v_{OE(S)}[mV]$            | 15*         | 25*     | _         | _              | 40        | 35*               | 13*              | 25    | 28    | 25        |

| $v_{OE(D)}[mV]$            | 50*         | 100*    | _         |                | 40        | 35*               | 25*              | 77    | 72    | 80        |

| $\Delta i_{O}[mA]$         | 0.18        | 20      | _         | _              | 1.0       | 4.5               | 1.0              | 1.0   | 10    | 1         |

| t <sub>R</sub> [μs]        | 2000*       | 100*    | _         |                | _         | _                 | ı                | 2500  | 100   | 9.6       |

| Max Efficiency [%]         | 83          | 95      | 87        | 87             | 89        | 90.2              | 84.4             | 86    | 88    | 88        |

| FoM [s <sup>-2</sup> ] *** | 180 k       | 200 M   | _         | _              | -         | _                 | -                | 2.4 M | 140 M | 1.2 G     |

<sup>\*</sup>Estimates from transient waveforms.

<sup>\*\*</sup>Estimates assuming  $v_S = 0.5v_{IN}$ ,  $P_S = v_S^2/4R_S$ .

<sup>\*\*\*</sup>The system desires small  $C_0$ ,  $t_R$ , and dynamic error  $v_{OE(D)}$  even under drastic  $\Delta i_O$ , so the Figure of Merit (FoM) is defined as: FoM =  $\Delta i_O / (C_O \times t_R \times v_{OE(D)})$ .

- Test, Integration and Packaging of MEMS/MOEMS, 2013, pp. 1-4.

- [9] X. Yu et al., "CMOS MEMS-based thermoelectric generator with an efficient heat dissipation path," in J. Micromechanics and Microengineering, vol. 22, no. 10, 2012.

- [10] H Glosch *et al.*, "A thermoelectric converter for energy supply," in *Sensors and Actuators A: Physical*, vol. 74, no. 1–3, pp. 246–250, 1999.

- [11] Z. Wang *et al.*, "Characterization of a bulk-micromachined membrane less in-plane thermopile," in *J. Electronic Materials*, vol. 40, no. 5, pp. 499–503, 2011.

- [12] P. P. Mercier et al., "A sub-nW 2.4 GHz transmitter for low data-rate sensing applications," in *IEEE J. Solid-State Circuits*, vol. 49, no. 7, pp. 1463–1474, July 2014.

- [13] Joseph Polastre, Jason Hill, and David Culler, "Versatile low power media access for wireless sensor networks," in *Proceedings of the 2nd International Conference on Embedded Networked Sensor Systems*, pp. 95–107. Association for Computing Machinery, New York, NY, USA.

- [14] M. Flatscher et al., "A bulk acoustic wave (BAW) based transceiver for an in-tire-pressure monitoring sensor node," in *IEEE J. Solid-State Circuits*, vol. 45, no. 1, pp. 167–177, Jan. 2010.

- [15] T-Mobile, "NB-IoT, LoRaWAN, Sigfox: an up-to-date comparison," Deutsche Telekom AG, Germany, Apr. 2021.

- [16] D. El-Damak and A. P. Chandrakasan, "A 10 nW-1 μW power management IC with integrated battery management and self-startup for energy harvesting applications," in *IEEE J. Solid-State Circuits*, vol. 51, no. 4, pp. 943–954, April 2016.

- [17] G. Chowdary, A. Singh and S. Chatterjee, "An 18 nA, 87% efficient solar, vibration and RF energy-harvesting power management system with a single shared inductor," in *IEEE J. Solid-State Circuits*, vol. 51, no. 10, pp. 2501–2513, Oct. 2016.

- [18] S. S. Amin and P. P. Mercier, "MISIMO: A multi-input single-inductor multi-output energy harvesting platform in 28-nm FDSOI for powering net-zero-energy systems," in *IEEE J. Solid-State Circuits*, vol. 53, no. 12, pp. 3407–3419, Dec. 2018.

- [19] H. Kim et al., "A 90.2% peak efficiency multi-input single-inductor multi-output energy harvesting interface with double-conversion rejection technique and buck-based dual-conversion mode," in *IEEE J. Solid-State Circuits*, vol. 56, no. 3, pp. 961–971, March 2021.

- [20] C. Liu et al., "Dual-source energy-harvesting interface with cycle-by-cycle source tracking and adaptive peak-inductor-current control," in IEEE J. Solid-State Circuits, vol. 53, no. 10, pp. 2741–2750, Oct. 2018.

- [21] G. Yu et al., "A 400 nW single-inductor dual-input-tri-output dc-dc buck-boost converter with maximum power point tracking for indoor photovoltaic energy harvesting," in *IEEE J. Solid-State Circuits*, vol. 50, no. 11, pp. 2758–2772, Nov. 2015.

- [22] Y. Wang et al., "A single-inductor dual-path three-switch converter with energy-recycling technique for light energy harvesting," in *IEEE J. Solid-State Circuits*, vol. 51, no. 11, pp. 2716–2728, Nov. 2016.

- [23] R. Damodaran Prabha and G. A. Rincón-Mora, "0.18-μm light-harvesting battery-assisted charger–supply CMOS system," in *IEEE Trans. Power Electronics*, vol. 31, no. 4, pp. 2950–2958, April 2016.

- [24] R. Damodaran Prabha, "Light-harvesting photovoltaic charger-supply microsystems," Ph.D. dissertation, Georgia Institute of Technology, Atlanta, May 2018.

- [25] T. Chang and G. A. Rincón-Mora, "Design of switched-inductor charging regulator for resistive on-chip thermoelectric generators," in *IEEE Trans. Circuits and Syst. II*, vol. 69, no. 6, pp. 2872–2876, Jun. 2022.

- [26] B. Razavi, "Design of analog CMOS integrated circuits," McGraw-Hill: Boston, MA, 2001.

- [27] K. Pelzers, H. Xin, E. Cantatore and P. Harpe, "A 2.18-pJ/conversion, 1656-µm² temperature sensor with a 0.61-pJ·K² FoM and 52-pW standby power," in *IEEE Solid-State Circuits Letters*, vol. 3, pp. 82–85, 2020.

- [28] V. Mangal and P. R. Kinget, "Sub-nW wake-up receivers with gate-biased self-mixers and time-encoded signal processing," in *IEEE J. Solid-State Circuits*, vol. 54, no. 12, pp. 3513–3524, Dec. 2019.

- [29] A. A. Blanco and G. A. Rincón-Mora, "Energy-harvesting microsensors: low-energy task schedule and fast drought-recovery design," in *IEEE International Midwest Symposium on Circuits and Systems*, 2016, pp. 1–4.

- [30] T. Chang and G. A. Rincón-Mora, "Lowest-v<sub>IN</sub> CMOS single-inductor boost charger: design, limits, and validation," in *IEEE Trans. Power Electronics*, vol. 37, no. 9, pp. 10808–10820, Sep. 2022.

[31] A. Patel and G. A. Rincón-Mora, "High power-supply-rejection (PSR) current-mode low-dropout (LDO) regulator," in *IEEE Trans. Circuits and Syst. II*, vol. 57, no. 11, pp. 868–873, Nov. 2010.