Fully Integrated Power-Saving Solutions for **DC-DC Converters Targeted for the Mobile**, **Battery-Powered Applications**

> Georgia Tech Analog Consortium **Industry Research Review**

> > Siyuan Zhou

Advisor: Prof. Gabriel A. Rincón-Mora

Analog Integrated Circuits Laboratory School of Electrical and Computer Engineering Georgia Institute of Technology March 21, 2003

## Abstract

### Motivation for Improving Efficiency in Mobile Applications

#### System-On-Chip (SOC)

Low power demands, low cost, and compactness make SOC suitable for portable, battery-powered applications, like cellular phones, pagers, laptop computers, MP3 players, PDAs, etc.

#### Low-voltage circuits

Required to satisfy the demand for single battery operation and the ever decreasing breakdown voltages of state-of-the-art technologies

#### Highly efficient, totally integrated DC-DC converters are strongly desired!

High Efficiency 📥 Low current drain 📥 Maximum battery life

- Total integration 📫 Small size and weight 📫 Optimum portability

#### Research Focus

Develop power-saving techniques for low voltage DC-DC converters suitable for *integrated solutions*.

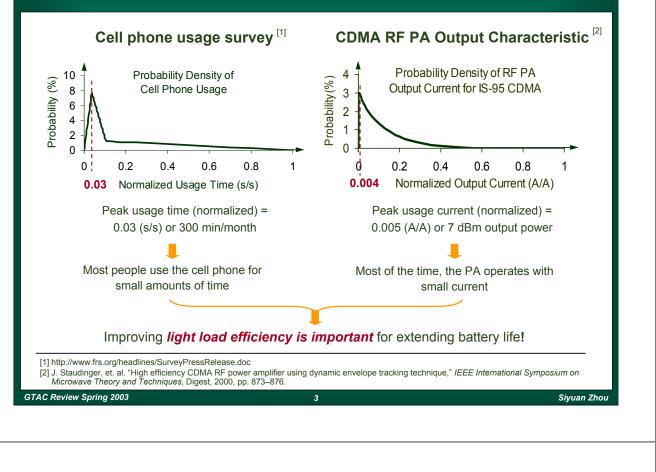

# Light load efficiency – Why is it important?

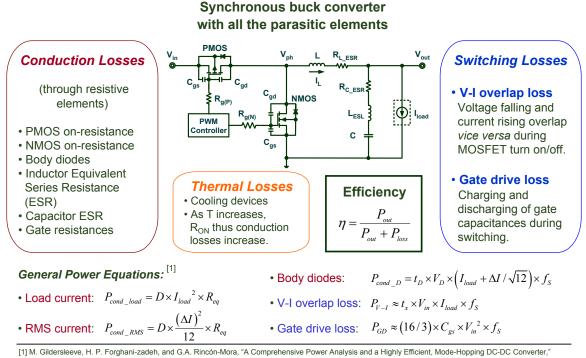

### **Power Losses – Where do they come from?**

[1] M. Gildersleeve, H. P. Forghani-zadeh, and G.A. Rincón-Mora, "A Comprehensive Power Analysis and a Highly Efficient, Mode-Hopping DC-DC Converter," IEEE Asia-Pacific Conference on ASIC, 2002, pp. 153–156.

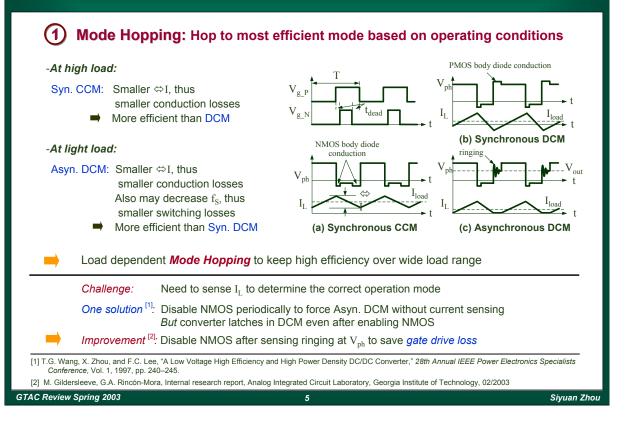

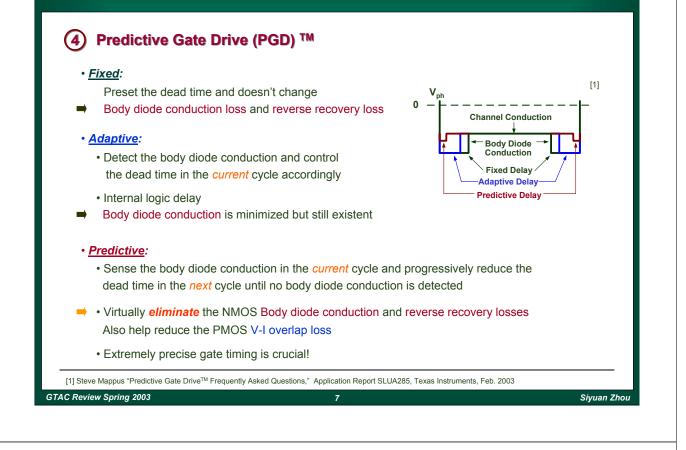

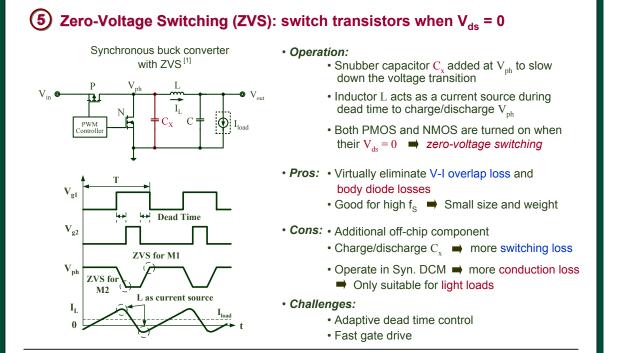

# How to improve efficiency? – Existing techniques

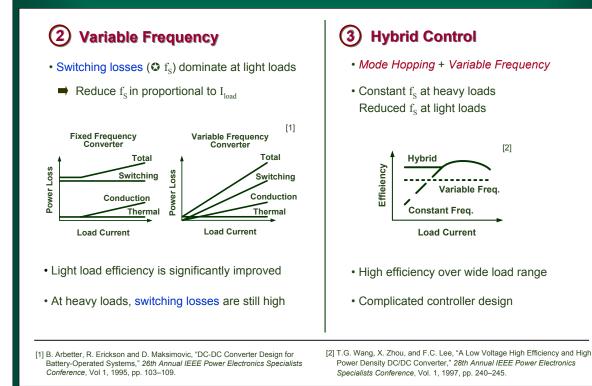

# How to improve efficiency? – Existing techniques

# How to improve efficiency? – Existing techniques

# How to improve efficiency? – Existing techniques

[1] A.J. Stratakos, S.R. Sanders and R. Brodersen, "A Low-Voltage CMOS DC-DC Converter for a Portable Battery-Operated System," 25th Annual IEEE Power Electronics Specialists Conference, Vol. 1, 1994, pp. 619–626.

### **Comparative Evaluation of Power Saving Techniques**

| Power<br>Losses<br>(mW) | Operation Condition (V <sub>in</sub> =3.3V) |                             |                                   |                             | Power Saving Techniques |                |                 |                  |        |

|-------------------------|---------------------------------------------|-----------------------------|-----------------------------------|-----------------------------|-------------------------|----------------|-----------------|------------------|--------|

|                         | $I_{load} = 1 A (CCM)$                      |                             | $I_{load} = 500 \text{ mA (DCM)}$ |                             | 1                       | 2              | 3               | 4                | 5      |

|                         | f <sub>s</sub> =<br>1 MHz                   | f <sub>s</sub> =<br>500 kHz | f <sub>s</sub> =<br>1 MHz         | f <sub>s</sub> =<br>500 kHz | Mode<br>Hop             | Vari.<br>Freq. | Hybrid<br>Ctrl. | PGD <sup>™</sup> | ZVS    |

| R <sub>PMOS</sub>       | 80 (35%)                                    | 79 (45%)                    | 24 (21%)                          | 30 (40%)                    | $\checkmark$            |                | $\checkmark$    |                  |        |

| R <sub>NMOS</sub>       | 28 (12%)                                    | 29 (17%)                    | 5 (4%)                            | 7 (9%)                      | $\checkmark$            |                | $\checkmark$    |                  |        |

| V <sub>Diode</sub>      | 22 (10%)                                    | 9 (5%)                      | 14 (13%)                          | 7 (9%)                      | Good                    | Good           | Better          | Best             | Better |

| R <sub>L_ESR</sub>      | 12 (5%)                                     | 12 (7%)                     | 4 (4%)                            | 4 (5%)                      | $\checkmark$            |                | $\checkmark$    |                  |        |

| R <sub>C_ESR</sub>      | 7 (3%)                                      | 8 (5%)                      | 5 (4%)                            | 5 (7%)                      | $\checkmark$            |                | $\checkmark$    |                  |        |

| R <sub>Gate</sub>       | 3 (1%)                                      | 2 (1%)                      | 3 (3%)                            | 1 (1%)                      | $\checkmark$            |                | $\checkmark$    |                  |        |

| V-I Ov.                 | 73 (32%)                                    | 33 (19%)                    | 52 (47%)                          | 19 (26%)                    |                         | Better         | Better          | Good             | Best   |

| Gate Dr.                | 5 (2%)                                      | 2 (1%)                      | 5 (4%)                            | 2 (3%)                      |                         | $\checkmark$   | $\checkmark$    |                  |        |

| Tot. Cond.              | 152(66%)                                    | 139(80%)                    | 55 (49%)                          | 55 (73%)                    | Best                    | OK             | Best            | Better           | Good   |

| Tot. Sw.                | 78 (34%)                                    | 35 (20%)                    | 57 (51%)                          | 20 (27%)                    | OK                      | Better         | Better          | Good             | Best   |

| Total Loss              | 230                                         | 174                         | 112                               | 75                          |                         |                |                 |                  |        |

| η                       | 86.4%                                       | 90%                         | 89.4%                             | 92.6%                       |                         |                |                 |                  |        |

#### GTAC Review Spring 2003

### Summary

9

- Rank of Losses:

- #1 Loss: PMOS Conduction Loss 👄

- #2 Loss: V-I Overlap Loss

- #3 Loss: NMOS Conduction Loss 👄

- #4 Loss: Body Diode Losses

- #6 Loss: Gate Drive Loss

- Reduce R<sub>PMOS</sub>

- Zero-Voltage Switching

- Reduce R<sub>NMOS</sub>

- ➡ Novel gate drive / dead time control

Siyuan Zhou

- Reduce R<sub>ESR</sub>

- Reduce parasitic C and/or f<sub>s</sub>

- To improve overall efficiency

improve light load efficiency!

- At heavy loads: Conduction Losses () f (current, ...) dominate At light loads: Switching Losses () f (frequency, ...) dominate

- *Hybrid Control* : best for reducing conduction losses

ZVS : best for reducing switching losses

Combine?