## Integrating Large Filter / Compensation Capacitors for SoC Applications

Abbas I. Poonawala Advisor: Gabriel A. Rincón-Mora Georgia Tech Analog Consortium March 21<sup>st</sup>, 2003

# **Capacitor Multipliers**

- WHY ? Capacitors supply large transient current and significantly reduce voltage fluctuations

- DEMAND: Low voltage, low power and small area

- **PROBLEM:** Large capacitors occupy too much silicon area

- GOAL: To design circuits that "multiply" the capacitance of small capacitors - Capacitor Multipliers

1

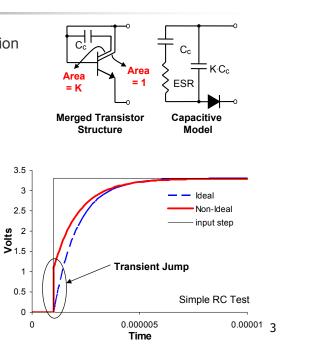

### **Capacitor Multiplication Techniques** I - Merged Transistor

s

C<sub>eff</sub> = (K+1)C<sub>c</sub> - Capacitor Multiplication Factor = "K+1"

### ADVANTAGES

- Easily integrated

- C<sub>eff</sub> dependant on K only and varies little with temperature and process

- No DC biasing requirement

### **DISADVANTAGES**

- For high K values, C<sub>eff</sub> increases but transistor mismatch degrades accuracy

- Undesired transient jump

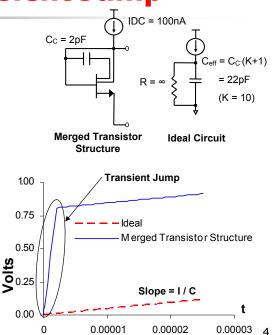

### I - Merged Transistor **Undesired Transient Jump**

- Ideal response to a constant current = I / C = 100nA/22pf

- Merged transistor response = 100nA/22.1pf

- Accuracy = 99.5 %

- However: undesired transient jump (Y-intercept of top trace) is ~0.8 V.

- The Y-intercept depends directly on the  $V_T$  of the transistors.

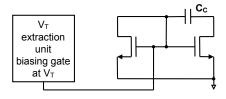

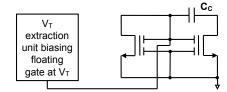

### I - Merged Transistor Eliminating Transient Jump

(Current Research)

- Transient jump occurs because parasitic capacitance C<sub>GS</sub> is charged first to V<sub>GS</sub> for transistors to start conducting current

- Biasing gate at V<sub>T</sub> will thus eliminate transient jump

- Simple V<sub>T</sub> extraction circuit used for biasing purposes

- Floating-Gate transistors used to store charge on gate

5

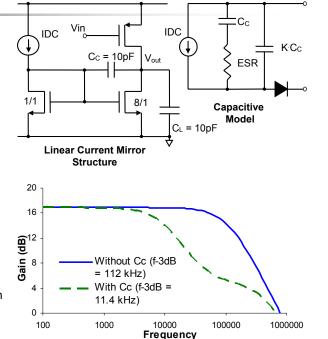

### II - Linear Mirror

- Without capacitor C<sub>c</sub> the dominant pole  $p_1 = \frac{1}{2}\pi \cdot R_{out} \cdot C_L = 112 \text{KHz}$

- With C<sub>C</sub> the dominant pole becomes  $p_2 = \frac{1}{2} \cdot \pi \cdot R_{out} \cdot C_{eff} = 11.4 \text{ KHz}$ , where  $C_{eff} = C_L + (K+1) \cdot C_C$

- $p_2 = p_1/10$  therefore  $C_{eff}$  is increased by a factor of 10, when  $C_C$  was added

#### **ADVANTAGES**

Ceff is dependant on K only and varies little with temperature and process

#### DISADVANTAGES

Adding C<sub>c</sub> will introduce a LHP Zero @

$Z = \frac{1}{2}\pi ESR C_C$

- Ceff increases with K but, transistor mismatch is a limiting factor

- Requires DC Bias current

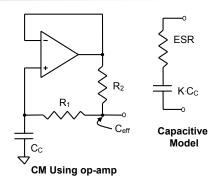

### III - Op-Amp

The node between R<sub>1</sub> and R<sub>2</sub> constitutes the terminal of an effective capacitance to ground given by

#### $C_{eff} = C_{C'}(R_1/R_2)$

Since R<sub>2</sub> determines the ESR of C<sub>eff</sub> a small value is desired for accuracy.

#### **ADVANTAGES**

- Large effective capacitances can be achieved at the expense of resistive die area

- Temperature dependence of the resistors cancel

### DISADVANTAGES

Circuit Complexity

7

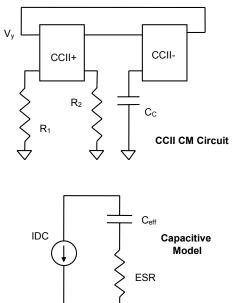

### **IV - Current Conveyor**

Assuming ideal CCIIs, the equivalent effective capacitance at V<sub>y</sub> is

#### $\mathbf{C}_{\mathrm{eff}} = \mathbf{C}_{\mathrm{C}}(\mathbf{R}_{2}/\mathbf{R}_{1})$

#### **ADVANTAGES**

- This circuit can provide capacitive gain of up to 10<sup>3</sup>.

- Higher gain is achieved by exploiting the current gain features of the two CCIIs.

#### DISADVANTAGES

- · A DC Bias current has to be supplied

- · Power dissipation increases with current gain

- · Circuit complexity

- CCII non-idealities diminish higher gain.

### **Summary Table**

| Technique                   | Merged<br>Transistor | I - Mirror | Op - Amp | CCII     |

|-----------------------------|----------------------|------------|----------|----------|

| Area                        | Lowest               | Low        | High     | Highest  |

| Undesired<br>Transient Jump | Yes                  | No         | No       | No       |

| Circuit Complexity          | Low                  | Low        | High     | Highest  |

| Ceff Terminals              | Floating             | Floating   | Floating | Floating |

| Temperature<br>Dependence   | Moderate             | Moderate   | Low      | Low      |

| Accuracy                    | Moderate             | Moderate   | High     | High     |

| Gain                        | Moderate             | Moderate   | High     | Highest  |

| DC Current Drain            | No                   | Yes        | No       | Yes      |

9

# Conclusion

- Merged transistor technique best in terms of area and circuit complexity

- Merged transistor structure has undesired transient jump associated with it

- Current conveyor technique best in terms of gain

- Current conveyor and linear mirror techniques require DC bias current