# ECE 4813

# Semiconductor Device and Material Characterization

### Dr. Alan Doolittle School of Electrical and Computer Engineering Georgia Institute of Technology

As with all of these lecture slides, I am indebted to Dr. Dieter Schroder from Arizona State University for his generous contributions and freely given resources. Most of (>80%) the figures/slides in this lecture came from Dieter. Some of these figures are copyrighted and can be found within the class text, *Semiconductor Device and Materials Characterization*. <u>Every serious</u> <u>microelectronics student should have a copy of this book!</u>

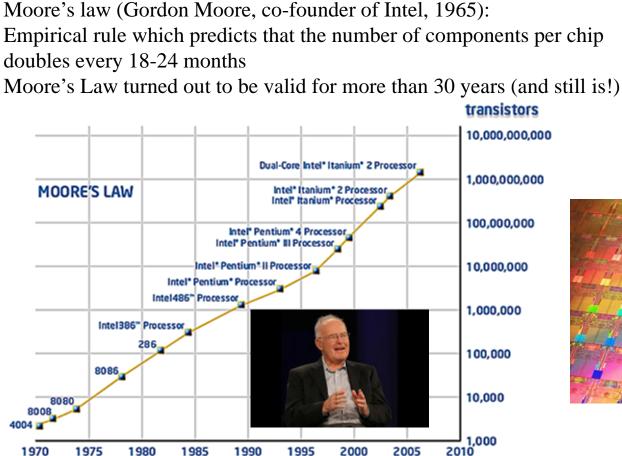

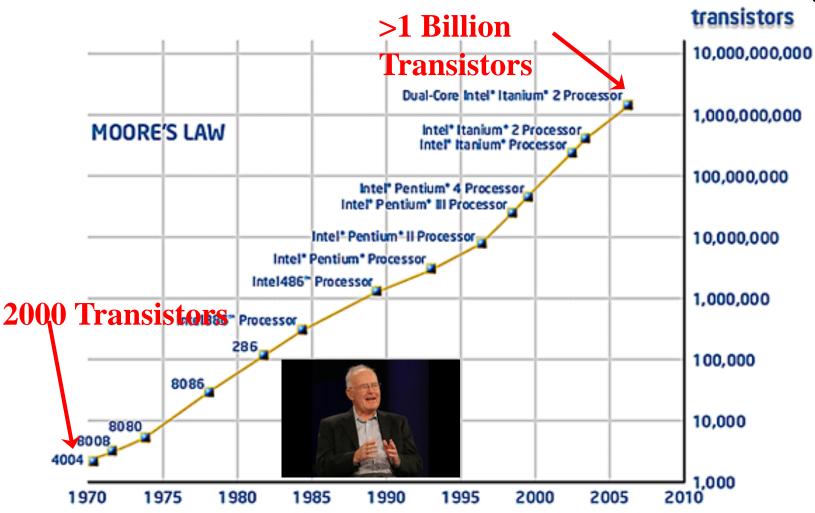

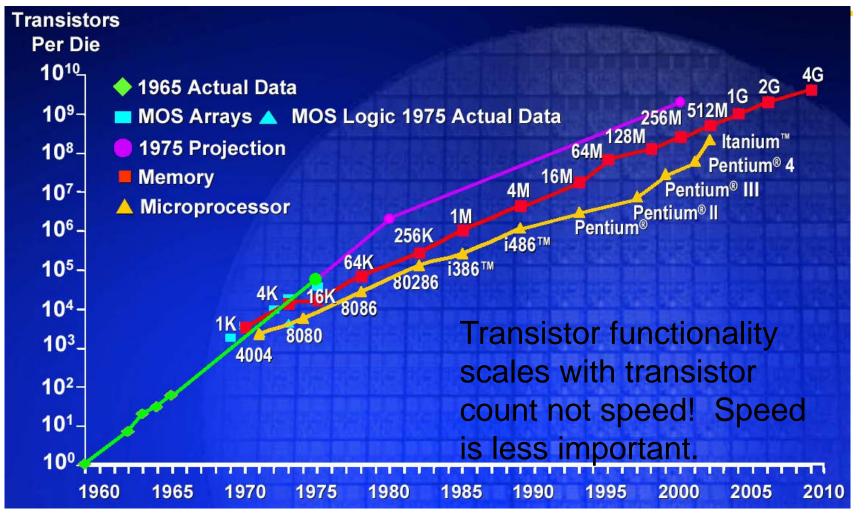

#### Moore's Law: The Growth of the Semiconductor Industry

Why do we need to know about Nano-electronic **Beorgia Tech** "materials" details? – A Case study of the evolution of the Transistor

Moore's Law: The Growth of the Semiconductor Industry

# Why do we need to know about Nano-electronic

"materials" details? – A Case study of the evolution of the Transistor

from G. Moore, ISSCC 2003

a Tecl

#### Why do we need to know about Nano-electronic Beorgia Tech "materials" details? – A Case study of the evolution of the Transistor

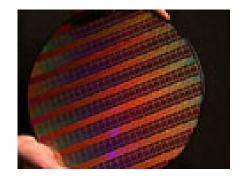

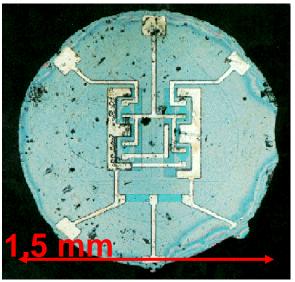

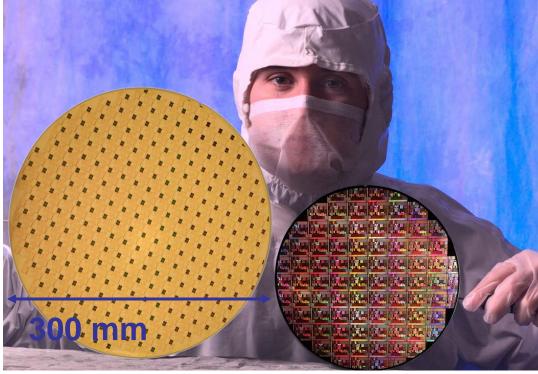

#### How did we go from 4 Transistors/wafer to Billions/wafer?

First Planar IC 1961, Fairchild http://smithsonianchips.si.edu/ IBM 200 mm and 300 mm wafer http://www-3.ibm.com/chips/photolibrary

#### Why do we need to know about Nano-electronic

"materials" details? – A Case study of the evolution of the Transistor

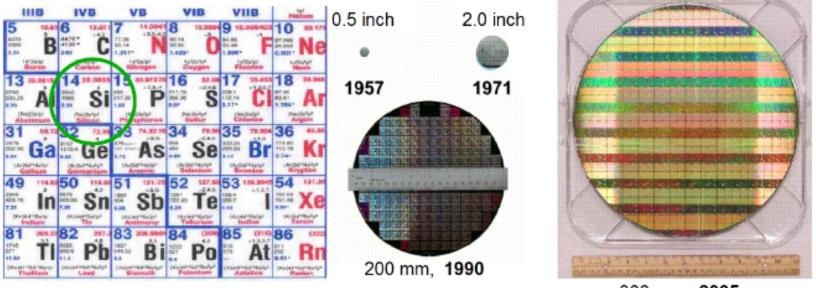

#### Some Facts About Silicon (Si):

- Si is a Group IV element, and crystallizes in the diamond structure

- Perfect Si crystals can be grown very large (12 inches by 8 feet!)

- Si can be made extremely pure (< .000001 ppm impurities!)</li>

- Si is very abundant and non-toxic (70% of the earth's crust are silicates!)

- Si oxidizes trivially to form one of nature's most perfect insulators (SiO<sub>2</sub>)

- Si is a great conductor of heat (better than many metals!)

300 mm, 2005

Slide after Dr. John Cressler

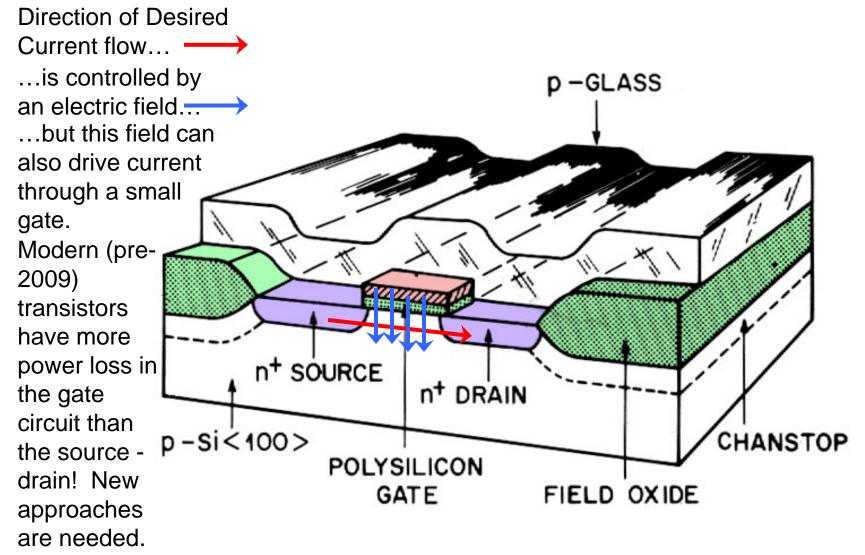

# The Basic Device in CMOS Technology is the MOSFET

# Why do we need to know about Nano-electronic

Why do Georgia Tech

**materials**" details? – A Case study of the evolution of the Transistor

#### Early MOSFET: SiO<sub>2</sub> Gate Oxide, Aluminum (AI) Source/Drain/Gate metals

Problem: As sizes shrank, devices became unreliable due to metallic spiking through the gate oxide.

Solution: Replace Metal Gate with a heavily doped poly-silicon.

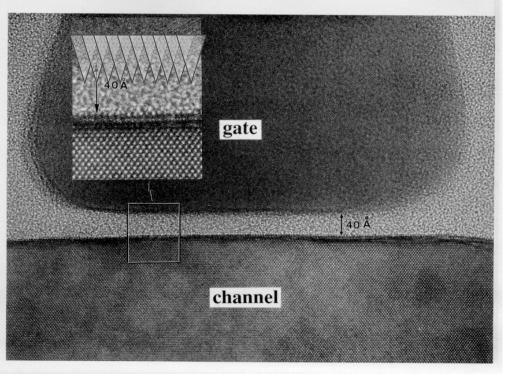

This change carried us for decades with challenges in fabrication (lithography) being the primary barriers that were overcome ...until... **Cross section of a MOSFET.** This high resolution transmission electron micrograph of a silicon Metal-Oxide-Semiconductor Field Effect Transistor shows the silicon channel and metal gate separated by a thin (40Å, 4nm) silicon-dioxide insulator. The inset shows a magnified view of the three regions, in which individual rows of atoms in the crystalline silicon can be distinguished. (Photograph courtesy of AT&T Bell Laboratories.)

#### Why do we need to know about Nano-electronic "Tech "materials" details? – A Case study of the evolution of the Transistor

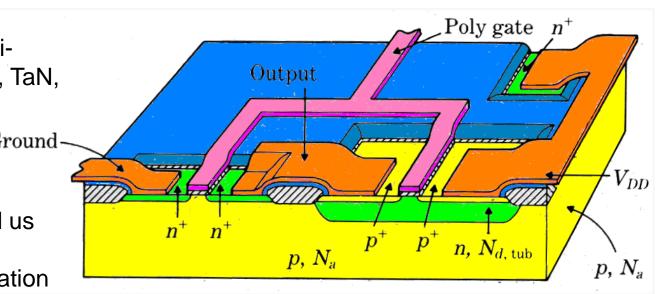

Semi-Modern MOSFET (late 1990's vintage): SiO<sub>2</sub> Gate Oxide, Polysilicon gate metals, metal source/drain contacts and Aluminum metal interconnects

Problem: As interconnect sizes shrank, Aluminum lines became too resistive leading to slow RC time constants

Solution: Replace Aluminum with multimetal contacts (TiN, TaN, etc...) and copper interconnects. Ground~

This change carried us for ~ 1 decade with challenges in fabrication (lithography) being the primary barriers that were overcome ...until...

Why do we need to know about Nano-electronic

**Gia Tech "materials" details?** – A Case study of the evolution of the Transistor

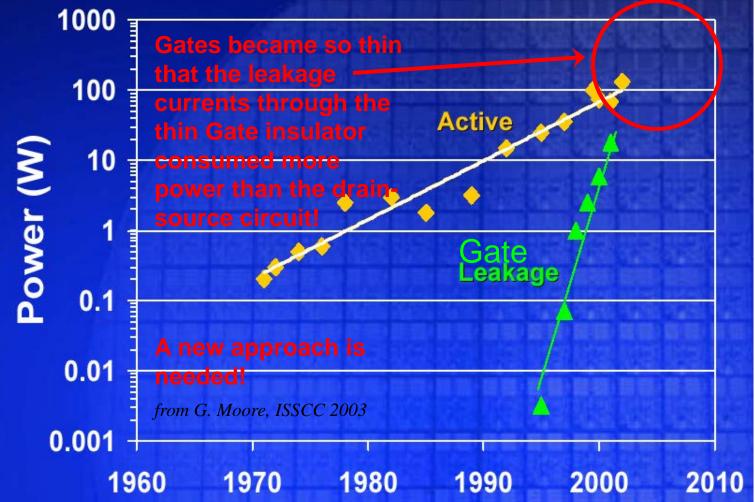

#### **Microprocessor Power Consumption**

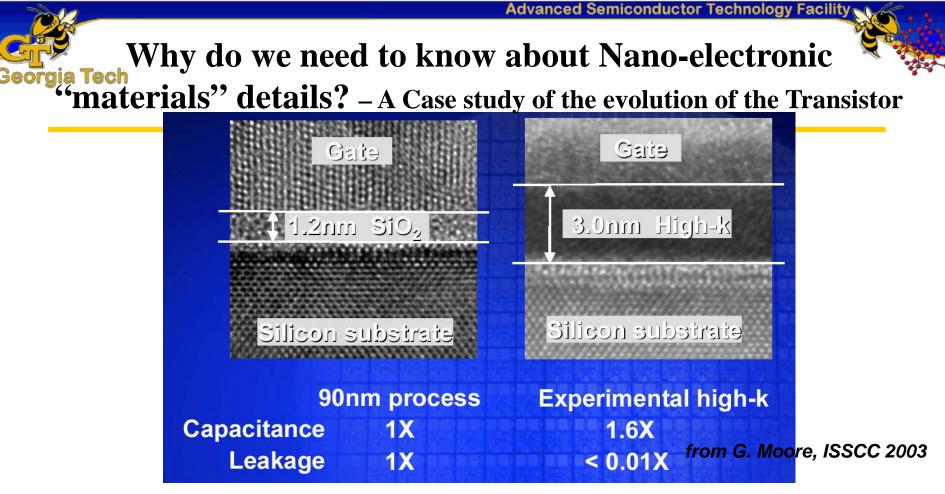

Gate leakage current can be dramatically lowered by increasing Gate insulator thickness but to do so without changing the channel conductivity, you have to increase the dielectric constant of the insulator. NEW GATE INSULATORS FOR THE FIRST TIME IN 60 YEARS!!!!

# Georgia Tech

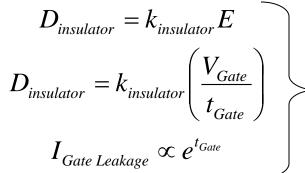

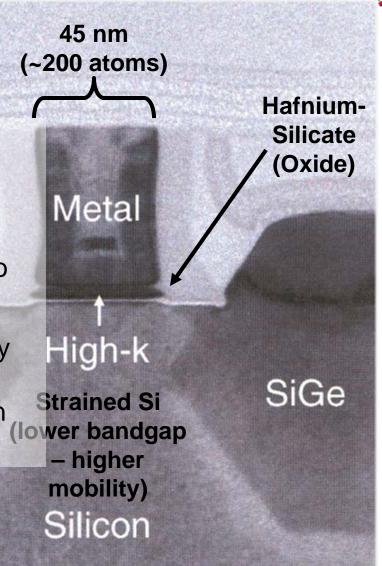

#### **2008 Vintage Intel Microprocessor**

#### •High K Gate Dielectric:

•K of SiO<sub>2</sub>~3.9< Hafnium Silicate ~? <  $HfO_2$ ~ 22

•Deviation from SiO<sub>2</sub> required reverting back to Metal Gates (no Poly-silicon)

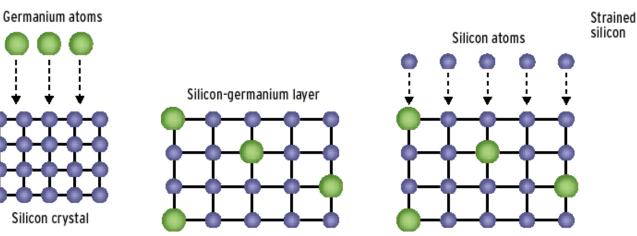

•Limited Speed of Silicon partially overcome by using SiGe to "mechanically strain" Si channel resulting in Energy Band structure modification that increases electron/hole mobility.

## **Strained Silicon MOSFET**

Strain

from IEEE Spectrum, 10/2002

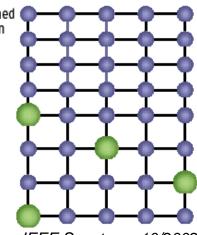

- Silicon in channel region is strained in two dimensions by placing a Si-Ge layer underneath (or more recently adjacent to) the device layer

- Strained Si results in changes in the energy band structure of conduction and valence band, reducing lattice scattering

- Benefit: increased carrier mobility, increased drive current (drain current)

Slide after Dr. Oliver Brandt

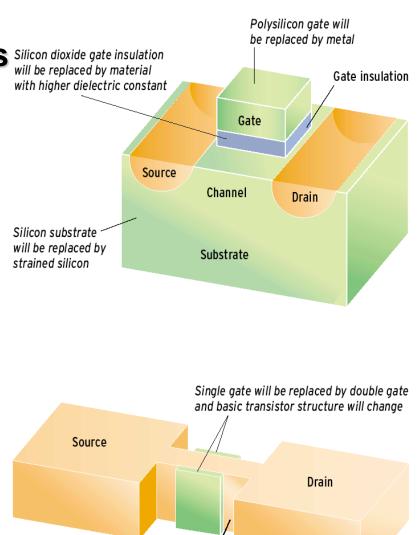

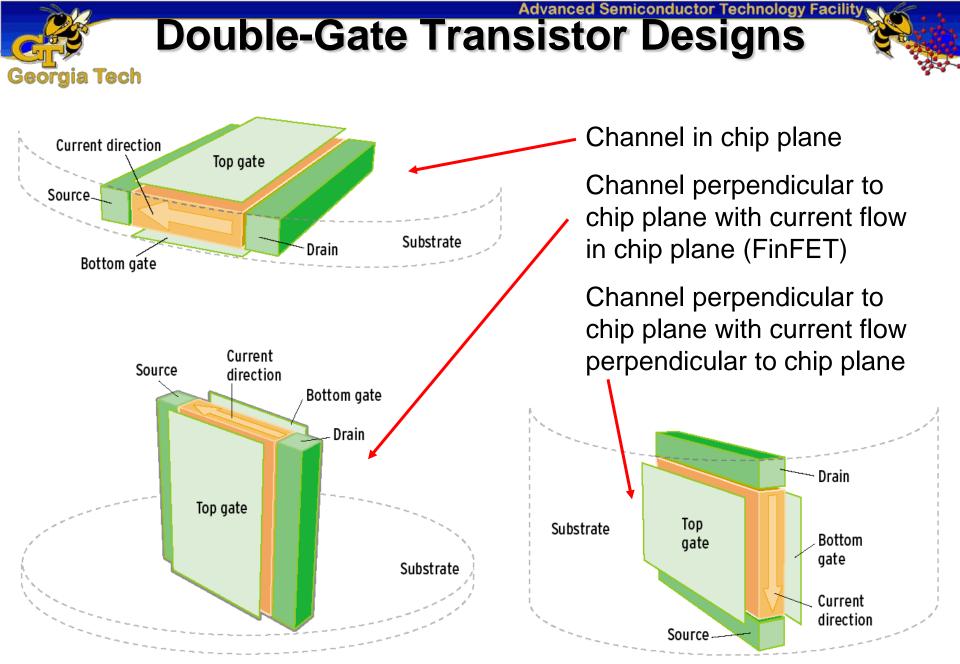

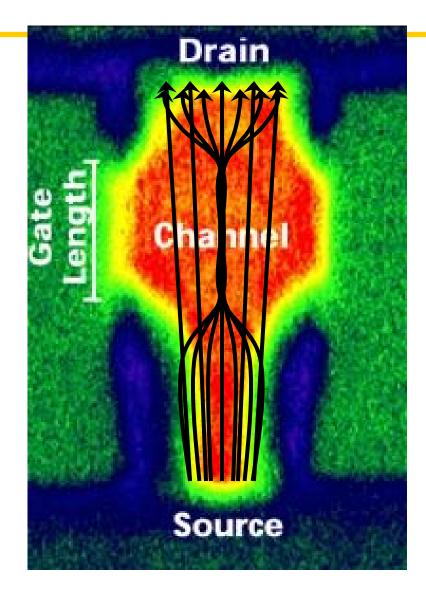

#### What is in the future? Double-Gate Transistors Silicon dioxide gate insulation

- Change of basic transistor structure by introducing a double gate (or more general enclose the channel area by the gate)

- Benefit: better channel control resulting in better device characteristics

- Challenge: double-gate transistors require completely new device structures with new fabrication challenges

from IEEE Spectrum, 10/2002

Channel

from IEEE Spectrum, 10/2002

Slide after Dr. Oliver Brandt

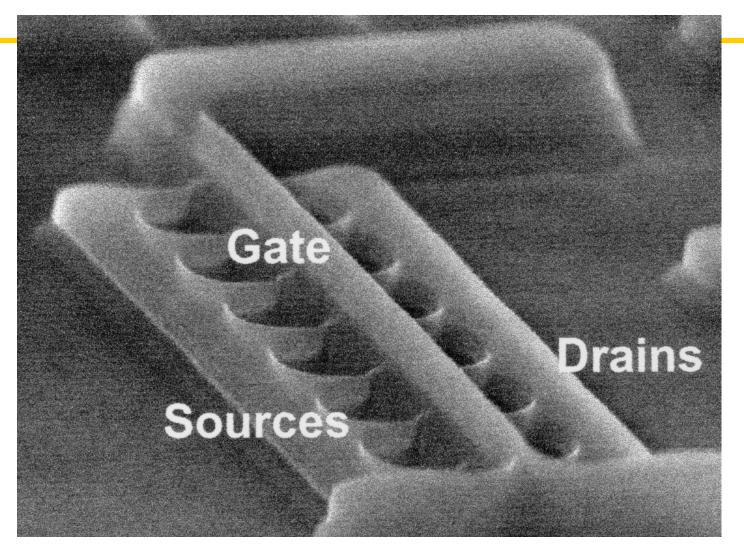

### **FinFET Double-Gate Transistor**

from http://www.intel.com/pressroom

Slide after Dr. Oliver Brandt

**C Georgia Tech** but now with the advantage of insulators. – Life is circular

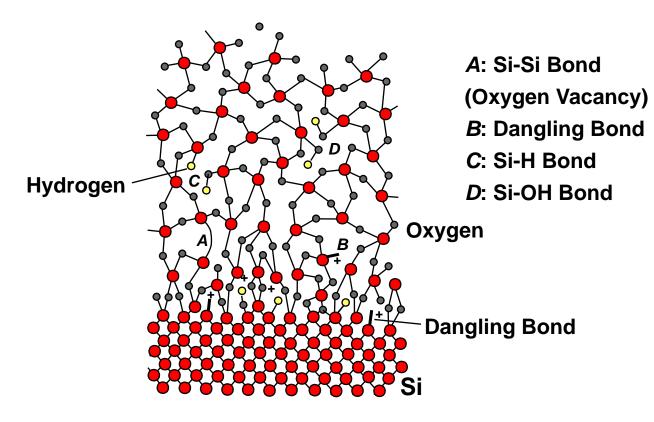

## SiO<sub>2</sub> and SiO<sub>2</sub>/Si Interface

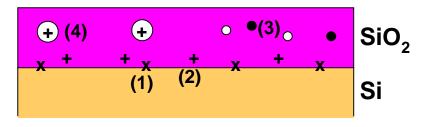

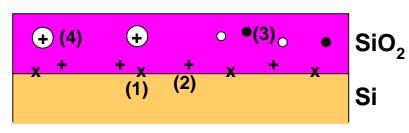

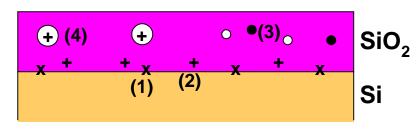

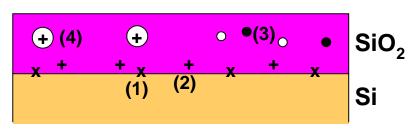

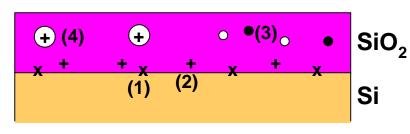

# Si, Si/SiO<sub>2</sub> interface, SiO<sub>2</sub> bulk, and oxide defect structure

### **Oxide Charges / Interface Traps**

Q=CV

| Charge                                                                                                                                    | Туре                        | Location                                   | Cause                                                  | Effect on Device                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------|

| 1) D <sub>it</sub> (cm <sup>-2</sup> eV <sup>-1</sup> ),<br>N <sub>it</sub> (cm <sup>-2</sup> ),<br>Q <sub>it</sub> ( C/cm <sup>2</sup> ) | Interface Trapped<br>Charge | SiO <sub>2</sub> /Si interface             | Dangling Bond, Hot<br>electron damage,<br>contaminants | Junction Leakage<br>Current, Noise,<br>Threshold Voltage<br>Shift, Subthreshold<br>Slope |

| 2) <i>N<sub>f</sub>, Q<sub>f</sub></i><br>(cm <sup>-2</sup> , C/cm <sup>2</sup> )                                                         | Fixed Charge                | Close to SiO <sub>2</sub> /Si<br>interface | Si⁺ (?)                                                | Threshold Voltage<br>Shift                                                               |

| 3) <i>N<sub>ot</sub>, Q<sub>ot</sub></i><br>(cm <sup>-2</sup> , C/cm <sup>2</sup> )                                                       | Oxide Trapped<br>Charge     | In SiO <sub>2</sub>                        | Trapped electrons<br>and holes                         | Threshold Voltage<br>Shift                                                               |

| 4) <i>N<sub>m</sub>,</i> Q <sub>m</sub><br>(cm <sup>-2</sup> , C/cm <sup>2</sup> )                                                        | Mobile Charge               | In SiO <sub>2</sub>                        | Na, K, Li                                              | Threshold Voltage<br>Shift (time<br>dependent)                                           |

# 1) Interface Trapped Charges

#### Can be either positive or negative charge

#### Due to:

- Structural Defects

- Oxidation Induced Defects

- Metallic Impurities

- Radiation induced broken bonds

- Radiation induced broken bonds

- Can be drastically improved by a low temperature (~450 C) anneal in a Hydrogen bearing gas.

# 2) Fixed Oxide Charges

- Generally positive charge and is related to oxidation conditions:

- Increases with decreasing oxidation temperature

- Can be reduced to a fixed (minimum value) by anneals in inert gases

- Can be effected by rapid cooling

# 3) Oxide Trapped Charges

Can be either positive or negative charge

#### Due to electrons or holes trapped in the oxide:

- Ionizing radiation (~>9 eV)

- Tunnel currents

Breakdown

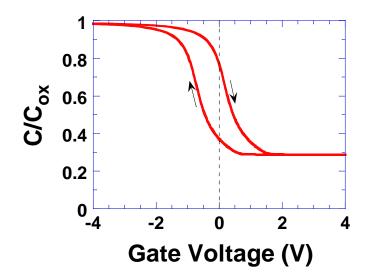

# 4) Mobile Charges

- Generally positive (sometimes negative but generally limited mobility if negative)

- Due to contaminants (Na, K, Li) in the oxide:

- Gate voltage slowly drives the charge across the oxide changing the threshold voltage and capacitance characteristics

- Can lead to hysteresis in the CV curve

- Can lead to time dependent threshold voltages

#### MOS Capacitor (MOS-C) can be used to determine

- Oxide charge

- Interface trapped charge

- Oxide thickness

- Flatband voltage

- Threshold voltage

- Substrate doping density

- Generation lifetime

- Recombination lifetime

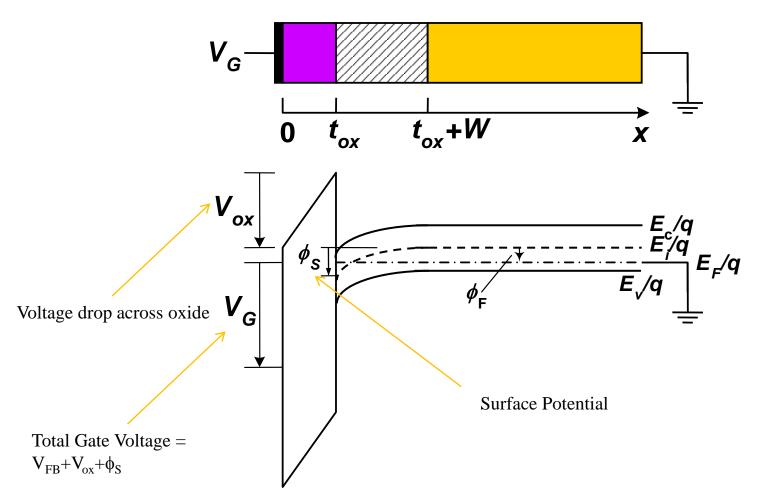

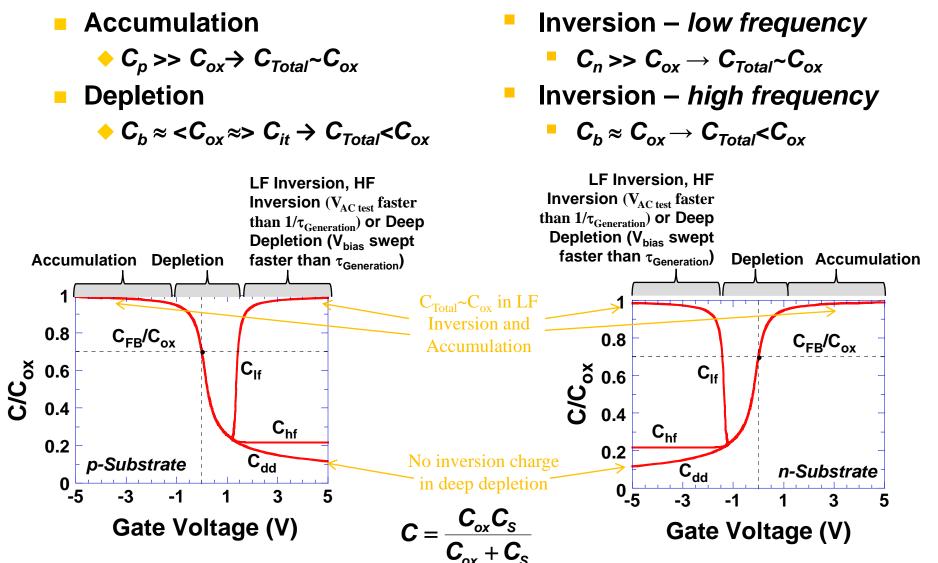

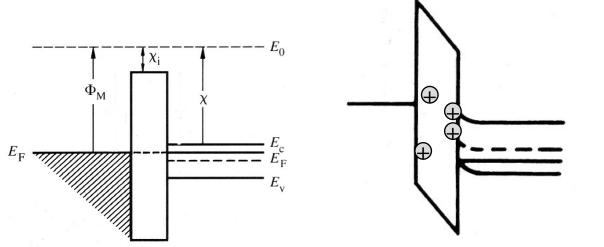

#### MOS capacitor cross section and band diagram

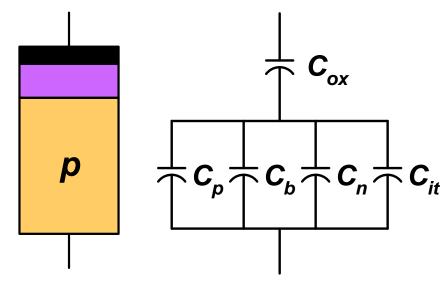

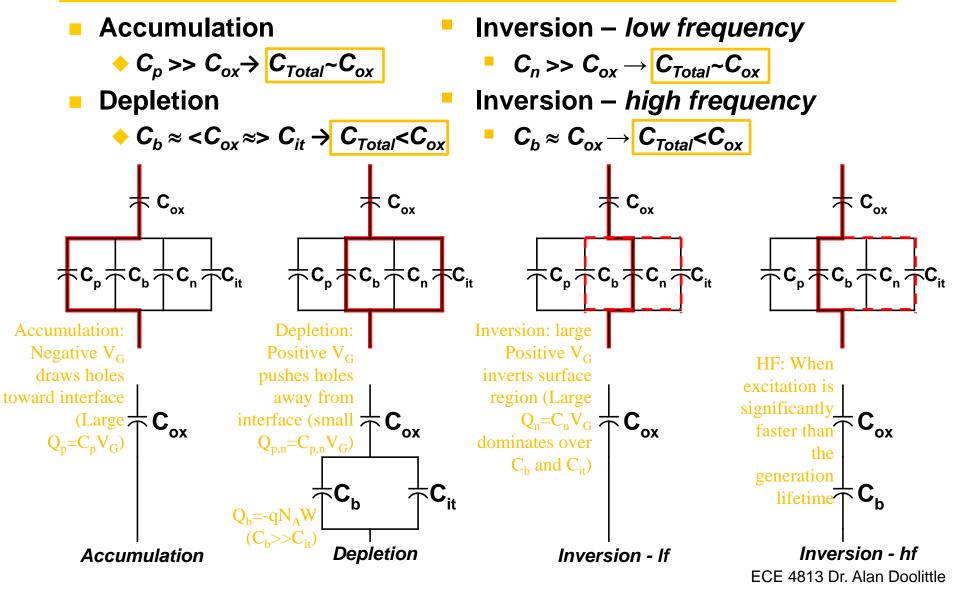

- Capacitance consists of

- C<sub>ox</sub>: oxide capacitance

- C<sub>p</sub>: accumulation capacitance

- C<sub>b</sub>: bulk (space-charge region) capacitance

- C<sub>n</sub>: inversion capacitance

- *C<sub>it</sub>*: interface trap capacitance

- Is generally given in units of Farads/cm<sup>2</sup>

The capacitance is

$$C = \frac{dQ_G}{dV_G}$$

The charge is

Assuming no oxide charge, gate charge = (-) semiconductor andinterface charge

$$\boldsymbol{Q}_{G} = -\boldsymbol{Q}_{s} - \boldsymbol{Q}_{it} = -(\boldsymbol{Q}_{p} + \boldsymbol{Q}_{b} + \boldsymbol{Q}_{n} + \boldsymbol{Q}_{it}) \boldsymbol{\boldsymbol{\nabla}}$$

This gives

Hole, space charge, electron, and interface charge densities.

$$C = \frac{dQ_{g}}{dV_{g}} = -\frac{dQ_{s} + dQ_{it}}{dV_{g}} = -\frac{dQ_{s} + dQ_{it}}{dV_{ox} + d\phi_{s}} \longleftarrow \text{Because } V_{FB} \text{ is fixed}$$

$$C = -\frac{1}{\frac{dV_{ox}}{dQ_{s} + dQ_{it}}} + \frac{d\phi_{s}}{dQ_{p} + dQ_{b} + dQ_{n} + dQ_{it}}$$

$$C = -\frac{1}{\frac{1}{\frac{1}{C_{ox}}} + \frac{1}{\frac{1}{C_{p} + C_{b}} + C_{n} + C_{it}}} = C = \frac{1}{\frac{1}{\frac{1}{C_{p}}} + \frac{1}{C_{p} + C_{b}} + C_{n} + C_{it}}}$$

ECE 4813 Dr. Alan Doc

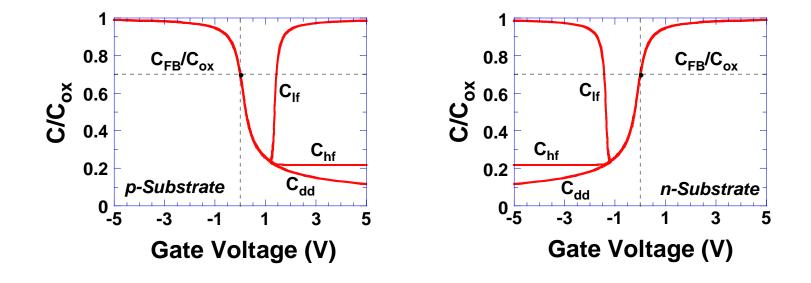

### **MOS Capacitance**

### **MOS Capacitance**

### MOS Capacitance – Generally Complex Mathematics

$$\begin{split} \mathbf{C}_{s,if} &= \hat{U}_{s} \frac{K_{s} \varepsilon_{0}}{2L_{Di}} \frac{\left[ e^{U_{F}} \left( 1 - e^{-U_{s}} \right) + e^{-U_{F}} \left( e^{U_{s}} - 1 \right) \right]}{F(U_{s}, U_{F})} \\ &\hat{U}_{s} &= \frac{\left| U_{s} \right|}{U_{s}}; U_{s} = \frac{\phi_{s}}{kT/q}; \ L_{Di} = \sqrt{\frac{K_{s} \varepsilon_{0} kT}{2q^{2} n_{i}}} \\ F(U_{s}, U_{F}) &= \sqrt{e^{U_{F}} \left( e^{-U_{s}} + U_{s} - 1 \right) + e^{-U_{F}} \left( e^{U_{s}} - U_{s} - 1 \right)} \\ \mathbf{C}_{s,hf} &= \hat{U}_{s} \frac{K_{s} \varepsilon_{0}}{2L_{Di}} \frac{\left[ e^{U_{F}} \left( 1 - e^{-U_{s}} \right) + e^{-U_{F}} \left( e^{U_{s}} - 1 \right) / (1 + \delta) \right]}{F(U_{s}, U_{F})} \\ &\delta &= \frac{\left( e^{U_{s}} - U_{s} - 1 \right) / F(U_{s}, U_{F})}{\int_{0}^{U_{s}} \frac{e^{U_{F}} \left( 1 - e^{-U} \right) \left( e^{U} - U - 1 \right)}{2[F(U_{s}, U_{F})]^{3}} dU} \\ &\mathbf{C}_{s,dd} &= \frac{C_{ox}}{\sqrt{\left[ 1 + 2(V_{G} - V_{FB}) / V_{0} \right] - 1}} \end{split}$$

### **MOS Capacitance**

$$\mathbf{C} = \frac{\mathbf{C}_{ox}\mathbf{C}_{S}}{\mathbf{C}_{ox} + \mathbf{C}_{S}}$$

$$V_{G} = V_{FB} + \phi_{S} + V_{ox} = V_{FB} + \phi_{S} + \hat{U}_{S} \frac{kTK_{s}t_{ox}F(U_{S}, U_{F})}{qK_{ox}L_{Di}}$$

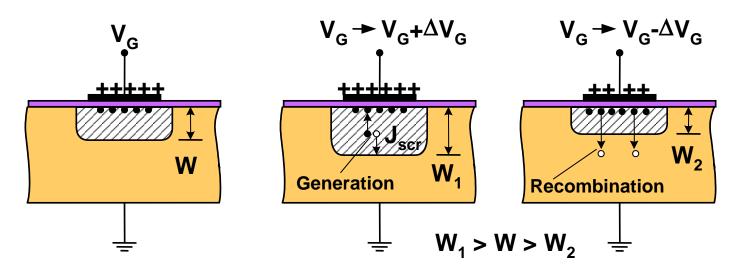

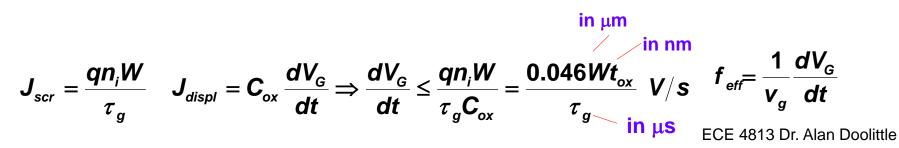

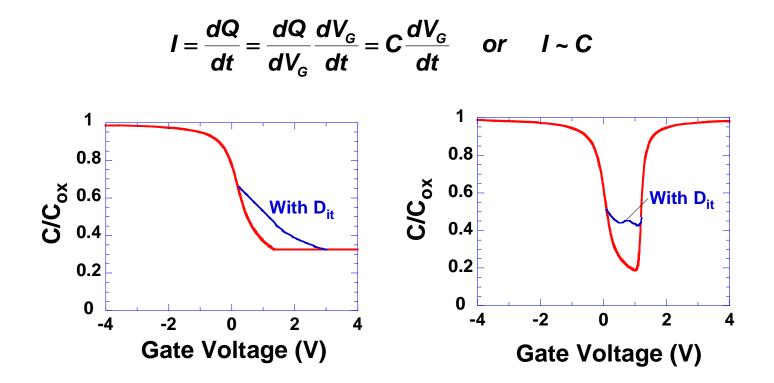

# **Low-Frequency Capacitance**

- To measure the low-frequency C-V<sub>G</sub> curve, the inversion carriers must be able to respond to both the ac gate voltage and the dc gate voltage sweep rate

- + ½ Cycle of V<sub>G</sub>: Driven displacement current (gate) must be less than the available space charge (generation) current

- <sup>1</sup>/<sub>2</sub> Cycle of V<sub>G</sub>: Recombination is fast enough to not be an issue

### **Low-Frequency Capacitance**

- The effective frequency is < 1 Hz</p>

- Very difficult to measure the capacitance

- Measure current

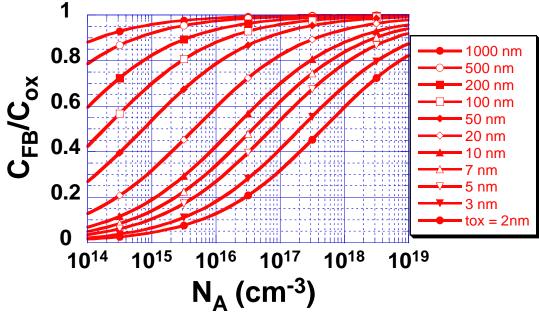

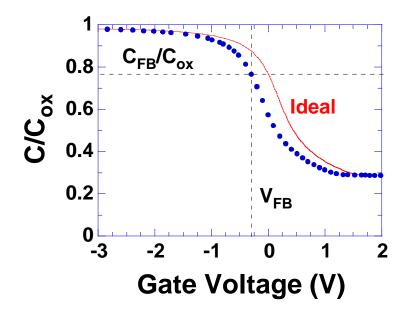

# Flatband Voltage (and Capacitance)

#### Most Junior level classes assume:

- A metal can be selected that aligns perfectly with the fermi-level in the semiconductor

- No charges exist in the Oxide

- These are generally not true (once again, we lied to you), leading to a "pre-bias" on the device

- This shifts the CV Curve and requires a voltage be applied to obtain "flat band" conditions.

- To determine V<sub>FB</sub>, one must compare the measured to theoretical CV curves and thus must know the theoretical flatband capacitance

The flatband voltage is that gate voltage at which the capacitance is the flatband capacitance

$$\boldsymbol{C}_{FB} = \frac{\boldsymbol{C}_{ox} \boldsymbol{C}_{S,FB}}{\boldsymbol{C}_{ox} + \boldsymbol{C}_{S,FB}}; \quad \boldsymbol{C}_{S,FB} = \frac{\boldsymbol{K}_{S} \boldsymbol{\varepsilon}_{0}}{\boldsymbol{L}_{D}}; \quad \boldsymbol{L}_{D} = \sqrt{\frac{\boldsymbol{K}_{S} \boldsymbol{\varepsilon}_{0} \boldsymbol{k} \boldsymbol{T}}{\boldsymbol{q}^{2} (\boldsymbol{p} + \boldsymbol{n})}} \approx \sqrt{\frac{\boldsymbol{K}_{S} \boldsymbol{\varepsilon}_{0} \boldsymbol{k} \boldsymbol{T}}{\boldsymbol{q}^{2} \boldsymbol{N}_{A}}}$$

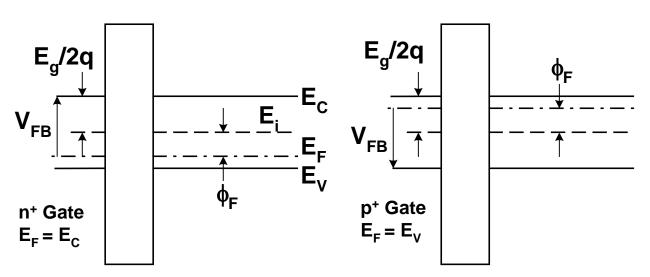

# Flatband Voltage

Flatband voltage depends on various gate, semiconductor, and oxide parameters

## **Work Function Difference**

- The work function difference,  $\phi_{MS}$ , depends on the Fermi level of the gate (polysilicon) and the substrate

- Assuming the gate is degenerately doped (i.e. fermi level is in the majority carrier band...

$$\phi_{\rm MS} = \phi_{\rm M} - \phi_{\rm S} = \phi_{\rm F}({\rm gate}) - \phi_{\rm F}({\rm substrate})$$

ECE 4813 Dr. Alan Doolittle

Advanced Semiconductor Technology Facility

t<sub>ox</sub>

# $Q_{f}, \phi_{MS}$ Measurements

Assume

$$Q_m = Q_{ot} = Q_{it} = 0$$

$V_{FB} = \phi_{MS} - \frac{Q_f}{C_{ox}} = \phi_{MS} - \frac{qN_f}{K_{ox}}$

#### Measure and plot V<sub>FB</sub> versus t<sub>ox</sub>

# **Mobile Charge**

#### Bia/-temperature stress (BTS)

It positive gate voltage to produce  $\mathcal{E}_{ox} \approx 10^6$  V/cm at  $^{\circ}$  °C for t = 5-10 min. Cool device with applied , measure C- $V_G$  at room temperature

at with negative gate voltage

The te voltage shift,  $\Delta V_{FB}$ , between the two curves is due to mobile charge

$$\mathbf{Q}_m = -\Delta V_{FB} \mathbf{C}_{ox}$$

ECE 4813 Dr. Alan Doolittle

### **Mobile Charge**

Triangular voltage sweep

♦ MOS-C is held at *T* = 200-300°C

+ High-frequency C -  $V_G$  and low-frequency I -  $V_G$  measured

$$I = \frac{dQ_{G}}{dt}$$

$$I = C_{If} \left(\alpha - \frac{dV_{FB}}{dt}\right)$$

$$\int_{-V_{G1}}^{V_{G1}} \left(\frac{I}{C_{If}} - \alpha\right) dV_{G} = -\alpha \left\{V_{FB}[t(V_{G2})] - V_{FB}[t(-V_{G1})]\right\}$$

$$-\alpha \left\{V_{FB}[t(V_{G2})] - V_{FB}[t(-V_{G1})]\right\} = \alpha \frac{Q_{m}}{C_{ox}}$$

$$\int_{-V_{G1}}^{V_{G1}} \left(\frac{I}{C_{If}} - \alpha\right) C_{ox} dV_{G} = -\alpha Q_{m}$$

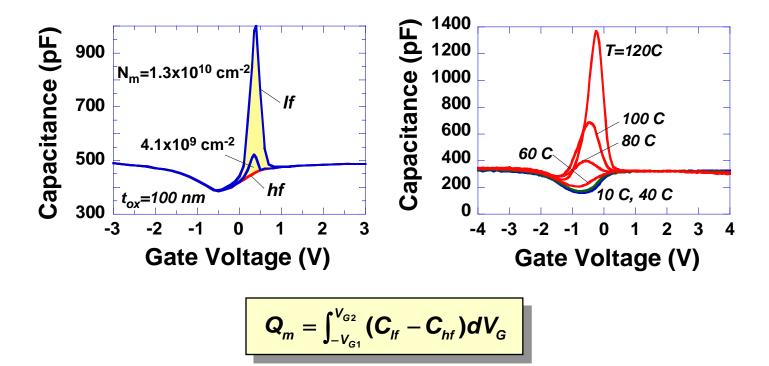

# **Mobile Charge**

#### Triangular Voltage Sweep (TVS)

- Measure hf and If C-V<sub>G</sub> curves simultaneously at  $T \approx 200^{\circ}$ C

- $Q_m$  = area between *If* and *hf* curves

- Suitable for gate oxides and interlevel dielectrics

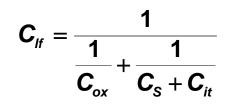

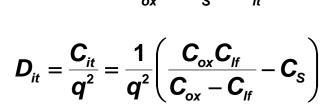

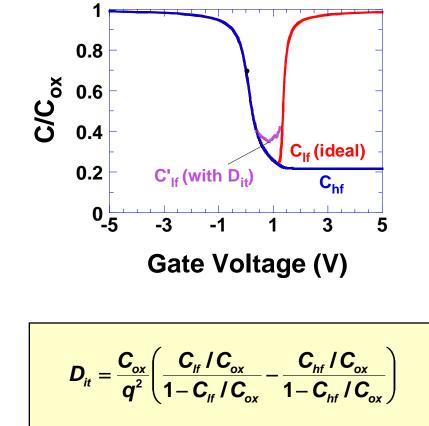

# Interface Trapped Charge

- Quasi-static method

- High-frequency and low-frequency C-V<sub>G</sub> curves are measured

$$\phi_{s} = \int_{V_{G1}}^{V_{G2}} \left( 1 - \frac{C_{If}}{C_{ox}} \right) dV_{G} + \Delta$$

$$\boldsymbol{C}_{\mathrm{S}} = \frac{\boldsymbol{C}_{\mathrm{ox}} \boldsymbol{C}_{\mathrm{hf}}}{\boldsymbol{C}_{\mathrm{ox}} - \boldsymbol{C}_{\mathrm{hf}}}$$

# **Quasistatic Method**

#### Current flow through oxide causes

- Interface state generation

- Oxide charge trappping

Data courtesy of W. Weishaar, Arizona State University

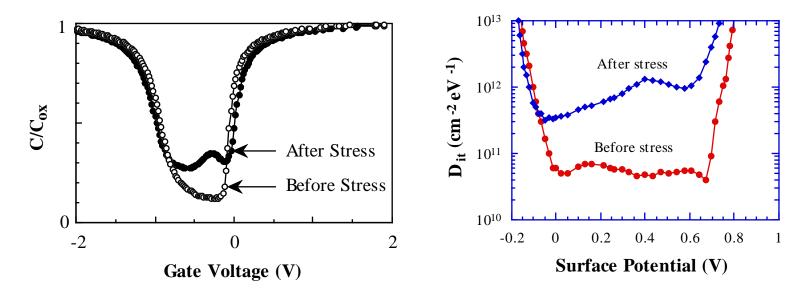

# Interface Trapped Charge

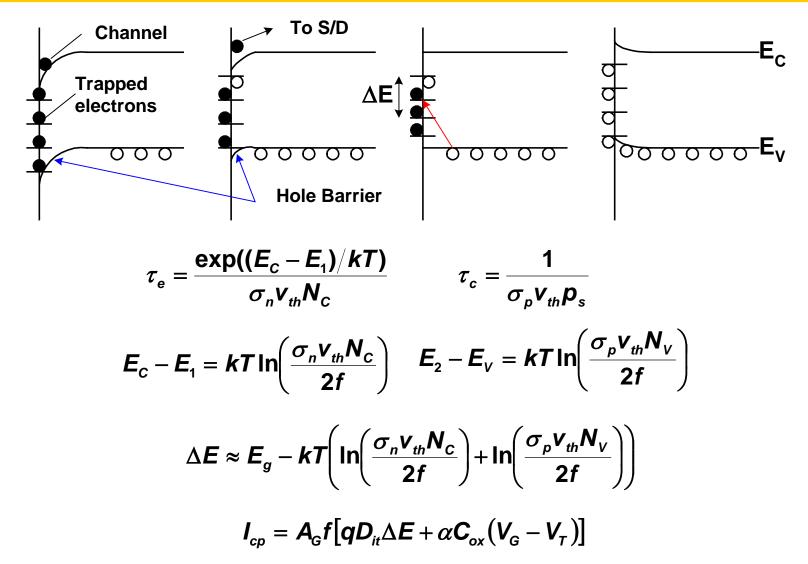

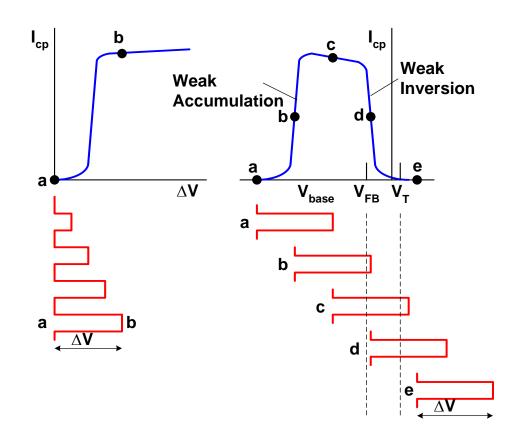

- Charge Pumping

- Uses MOSFET

- Apply periodically varying gate voltage

- Measure resulting current at the substrate or source/drain

Advanced Semiconductor Technology Facility 🛁

### **Charge Pumping**

ECE 4813 Dr. Alan Doolittle

# **Charge Pumping**

#### Bilevel

Keep baseline constant, vary pulse height

Vary baseline, keep pulse height constant

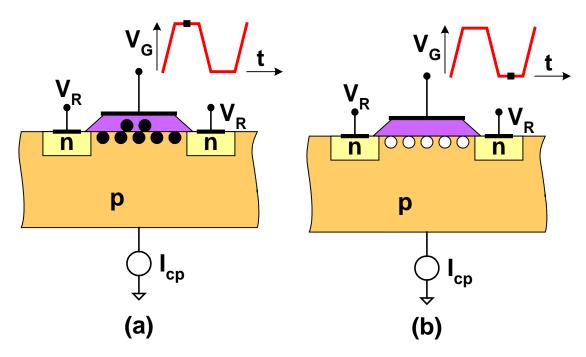

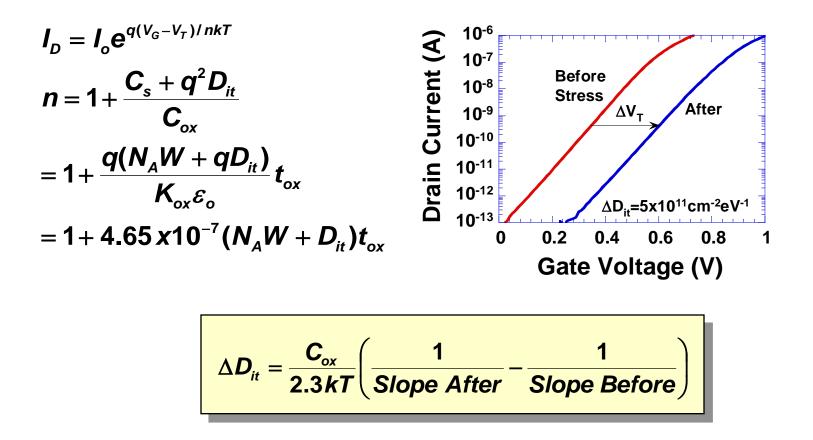

# MOSFET Subthreshold $I_D - V_G$

- Below  $V_T$ ,  $I_D$  depends exponentially on  $V_G$

- Slope change due to stress is very small for thin oxides

# **Review Questions**

- Name the four main charges in the oxide

- How is the low-frequency capacitance measured?

- What is the flatband voltage and flatband capacitance?

- Describe charge pumping.

- How does the subthreshold slope yield the interface trap density?