## Homework Assignment No. 2

Due Wednesday, January 22, 2003 in class

Problem 1 - (10 points)

Problem 5.20 of Gray and Meyer. The SPICE parameters to use for this problem are:

.MODEL NPN NPN RB=200 BF=80 IS=1E-18 VAF=130 .MODEL PNP PNP RB=300 BF=20 IS=1E-18 VAF=50 .MODEL PMOS PMOS KP=26U LAMBDA=0.0125 VTO=-0.7 LD=0

Use the following table to summarize your answers for easier grading. (a). Device Currents

|                 | Hand Calculations | SPICE Simulations |  |

|-----------------|-------------------|-------------------|--|

| I <sub>C1</sub> |                   |                   |  |

| I <sub>C2</sub> |                   |                   |  |

| I <sub>C3</sub> |                   |                   |  |

| I <sub>C5</sub> |                   |                   |  |

| I <sub>C6</sub> |                   |                   |  |

| I <sub>D1</sub> |                   |                   |  |

| I <sub>D2</sub> |                   |                   |  |

| I <sub>D3</sub> |                   |                   |  |

|                 |                   |                   |  |

| (b) $V =$       | V                 | _                 |  |

(b).  $V_{o(max)} =$ \_\_\_\_\_  $V_{o(mim)} =$ \_\_\_\_\_

P<sub>max</sub> = \_\_\_\_\_

(c). SPICE Results

- A plot of the DC transfer characteristic and mark on your results where clipping begins to occur.

- Plots of  $i_{C1}$ ,  $i_{C2}$ , and  $i_{D2}$  for  $v_o = 2V$  peak and  $v_o = 4V$  peak. Assume a signal frequency of 10 KHz. (Note: you will have to apply the appropriate dc bias and signal amplitude to achieve the desired output conditions.)

- Also use SPICE to compute the THD of the output voltage for both the 2V and 4 V conditions.

|                       | Hand Calculations | SPICE Simulations |  |

|-----------------------|-------------------|-------------------|--|

| Clipping              |                   |                   |  |

| max                   |                   |                   |  |

| min                   |                   |                   |  |

| THD of v <sub>o</sub> |                   |                   |  |

| 2V peak               | NA                |                   |  |

| 4V peak               | NA                |                   |  |

## Problem 2 - (10 points)

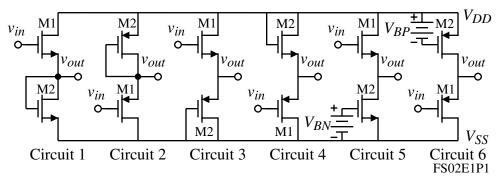

Six versions of a source follower are shown below. Assume that  $K'_N = 2K'_P$ ,  $\lambda_P = 2\lambda_N$ , all W/L ratios of all devices are equal, and that all bias currents in each device are equal. Neglect bulk effects in this problem and assume no external load resistor. Identify which circuit or circuits have the following characteristics: (a.) highest small-signal voltage gain, (b.) lowest small-signal voltage gain, (c.) the highest output resistance, (d.) the lowest output resistance, (e.) the highest  $v_{out}(\max)$  and (f.) the lowest  $v_{out}(\max)$ .

## Problem 3 - (10 points)

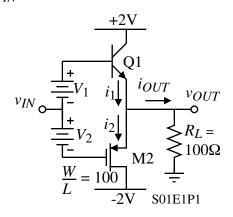

A push-pull follower is shown which uses an NPN BJT and a p-channel MOSFET. In this problem, ignore the bulk effect, the channel length modulation, and the Early voltage. The parameters for the NPN BJT are  $_{-F} = 100$ ,  $I_s = 10$ fA and  $V_t = 25.9$ mV. The model parameters for the PMOS are  $K_P' = 50\mu A/V^2$  and  $V_T = -0.7V$ . (a.) Find the value of the dc batteries,  $V_1$  and  $V_2$ , which will cause 100 $\mu$ A to flow in Q1 and M2 when the dc value of  $v_{IN} = 0$ VDC. (b.) Find the small-signal input resistance, output resistance and voltage gain when the dc value of  $v_{IN} = 0$ VDC.

## Problem 4 (40 points) - Design Problem #1

You are to design a CMOS output amplifier having a single-ended input and singleended output and a voltage gain of +1. This amplifier is to use  $\pm 2V$  power supplies and all W/L values should be between 1 and 100. You may only use MOSFETs or substrate or vertical BJTs (only one type, NPN) in your design with the exception of a load capacitor  $(C_L)$  and load resistor  $(R_L)$ . You should use the following model parameters for SPICE. Use  $\beta_F = 100$  and  $I_s = 10$ fA for the BJT.

|      | <i>K</i> '<br>(μΑ/V <sup>2</sup> ) | $V_T(\mathbf{V})$ | $\gamma(\sqrt{V})$ | $2\phi_F(V)$ | $\lambda (V^{-1})$                   |

|------|------------------------------------|-------------------|--------------------|--------------|--------------------------------------|

| NMOS | 110                                | 0.7               | 0.4                | 0.7          | $0.04(L=1\mu m)$<br>$0.01(L=2\mu m)$ |

| PMOS | 50                                 | -0.7              | 0.57               | 0.8          | 0.05(L=1µm)<br>0.01(L=2µm)           |

The various definitions used in the specifications of this design are:

1.) Slew rate (*SR*) is the smallest  $\pm$ output voltage rate across a 1nF load capacitance when the output voltage is between  $\pm$ 1V.

2.) The peak output voltage  $(V_P)$  is the minimum ±deviation from the quiescent output voltage when a sinusoid is applied to the input and a 100 $\Omega$  resistor is attached to the ouput.

3.) Efficiency in percent  $(\eta)$  is defined as

$$\eta = \left(\frac{\text{Power to the load resistor of } 100\Omega}{\text{Power from the supplies}}\right) \times 100$$

4.) Voltage gain  $(A_v)$  is the output voltage (peak-to-peak) over the input voltage (peak-to-peak) when the output is loaded with a 100 $\Omega$  load resistor.

Your score for this problem will be determined as follows:

SCORE =  $1.0 \times 10^{6} \cdot \min[SR, 10V/\mu s] + 10 \cdot \min[V_{P}, 1] + 0.4 \cdot \min[\eta, 25] + \frac{10}{|A_{v}-1| + 1}$