## LECTURE 050 – COMMON SOURCE AND EMITTER OUTPUT STAGES

### (READING: GHLM - 384-398, AH - 218-221)

### **Objective**

The objective of this presentation is:

Show how to design stages that

- 1.) Provide sufficient output power in the form of voltage or current.

- 2.) Avoid signal distortion.

- 3.) Be efficient

- 4.) Provide protection from abnormal conditions (short circuit, over temperature, etc.)

# **Outline**

- Common source stage

- Common emitter stage

- Summary

ECE 6412 - Analog Integrated Circuits and Systems II

© P.E. Allen - 2002

Lecture 050 – CE and CS Output Stages (12/31/01)

Page 050-2

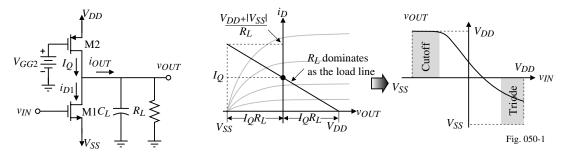

#### COMMON SOURCE OUTPUT STAGE Current source load inverter

A Class A circuit has current flow in the MOSFETs during the entire period of a sinusoidal signal.

Characteristics of Class A amplifiers:

- Unsymmetrical sinking and sourcing

- Linear

- Poor efficiency

$$\text{Efficiency} = \frac{P_{RL}}{P_{Supply}} = \frac{\frac{v_{OUT}(\text{peak})^2}{2R_L}}{(V_{DD} - V_{SS})I_Q} = \frac{\frac{v_{OUT}(\text{peak})^2}{2R_L}}{(V_{DD} - V_{SS})\left(\frac{(V_{DD} - V_{SS})}{2R_L}\right)} = \left(\frac{v_{OUT}(\text{peak})}{V_{DD} - V_{SS}}\right)^2$$

Maximum efficiency occurs when  $v_{OUT}(\text{peak}) = V_{DD} = |V_{SS}|$  which gives 25%.

ECE 6412 - Analog Integrated Circuits and Systems II

#### **Specifying the Performance of a Common Source Amplifier**

Output resistance:

$$r_{out} = \frac{1}{g_{ds1} + g_{ds2}} = \frac{1}{(\lambda_1 + \lambda_2)I_D}$$

Current:

• Maximum sinking current is,

$$\bar{I}_{OUT} = \frac{K'_1 W_1}{2L_1} (V_{DD} - V_{SS} - V_{T1})^2 - I_Q$$

• Maximum sourcing current is,

$$I_{OUT}^{+} = \frac{K_{2}^{\prime} W_{2}}{2L_{2}} (V_{DD} - V_{GG2} - |V_{T2}|)^{2} \le I_{Q}$$

**Requirements:**

- Want  $r_{out} \ll R_L$

- $|I_{OUT}| > C_L \cdot SR$

- $|I_{OUT}| > \frac{v_{OUT}(\text{peak})}{R_L}$

The maximum current will be determined by **both** the current required to provide the necessary slew rate ( $C_L$ ) and the current required to provide a voltage across the load resistor ( $R_L$ ).

ECE 6412 - Analog Integrated Circuits and Systems II

```

Lecture 050 – CE and CS Output Stages (12/31/01)

```

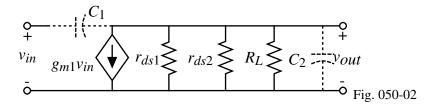

### **Small-Signal Performance of the Class A Amplifier**

Although we have considered the small-signal performance of the Class A amplifier as the current source load inverter, let us include the influence of the load.

The modified small-signal model:

The small-signal voltage gain is:

$$\frac{v_{out}}{v_{in}} = \frac{-g_{m1}}{g_{ds1} + g_{ds2} + G_L}$$

The small-signal frequency response includes:

A zero at

$$z = \frac{g_{m1}}{C_{gd1}}$$

and a pole at

$$p = \frac{-(g_{ds1} + g_{ds2} + G_L)}{C_{gd1} + C_{gd2} + C_{bd1} + C_{bd2} + C_L}$$

ECE 6412  $\,$  - Analog Integrated Circuits and Systems II  $\,$

Page 050-4

© P.E. Allen - 2002

### Example 5.5-1 - Design of a Simple Class-A Output Stage

Use the values of  $K_N$ '=110µA/V<sup>2</sup>,  $K_P$ '=50µA/V<sup>2</sup>,  $V_{TN}$ =0.7V and  $V_{TP}$ =-0.7V and design the *W/L* ratios of M1 and M2 so that a voltage swing of ±2 volts and a slew rate of  $\cong$ 1 volt/µs is achieved if  $R_L = 20 \text{ k}\Omega$  and  $C_L = 1000 \text{ pF}$ . Assume that  $V_{DD} = |V_{SS}| = 3$  volts and  $V_{GG2} = 0$  volts. Let the channel lengths be 2 µm and assume that  $C_{gd1} = 100 \text{ FF}$ . Solution

Let us first consider the effects of  $R_L$  and  $C_L$ .

$$i_{OUT}(\text{peak}) = \frac{\pm 2V}{20k\Omega} = \pm 100\mu\text{A}$$

and  $C_L \cdot SR = 10^{-9} \cdot 10^6 = 1000\mu\text{A}$

Since the slew rate current >> the current for  $R_L$ , we can safely assume that all of the current supplied by the inverter is available to charge  $C_L$ .

Using a value of  $\pm 1$  mA,

$$\frac{W_1}{L_1} = \frac{2(I_{OUT} + I_Q)}{K_N'(V_{DD} + |V_{SS}| - V_{TN})^2} = \frac{4000}{110 \cdot (5.3)^2} \approx \frac{3\mu m}{2\mu m}$$

and

$$\frac{W_2}{L_2} = \frac{2I_{OUT}^+}{K_P'(V_{DD} - V_{GG2} - |V_{TP}|)^2} = \frac{2000}{50 \cdot (2.3)^2} \approx \frac{15\mu m}{2\mu m}$$

The small-signal performance of this amplifier is,  $A_v = -8.21 \text{ V/V}$  (includes  $R_L = 20 \text{k}\Omega$ )

ECE 6412 - Analog Integrated Circuits and Systems II

Lecture 050 – CE and CS Output Stages (12/31/01)

# **Broadband Harmonic Distortion**

The linearity of an amplifier can be characterized by its influence on a pure sinusoidal input signal.

Assume the input is,  $V_{in}(\omega) = V_p \sin(\omega t)$

The output of an amplifier with distortion will be

$$V_{out}(\omega) = a_1 V_p \sin(\omega t) + a_2 V_p \sin(2\omega t) + \dots + a_n V_p \sin(n\omega t)$$

*Harmonic distortion (HD)* for the *i*th harmonic can be defined as the ratio of the magnitude of the *i*th harmonic to the magnitude of the fundamental.

For example, second-harmonic distortion would be given as

$$HD_2 = \frac{a_2}{a_1}$$

*Total harmonic distortion (THD)* is defined as the square root of the ratio of the sum of all of the second and higher harmonics to the magnitude of the first or fundamental harmonic. Thus, *THD* can be expressed as

$$THD = \frac{[a_2^2 + a_3^2 + \dots + a_n^2]^{1/2}}{a_1}$$

The distortion of the class A amplifier is good for small signals and becomes poor at maximum output swings because of the nonlinearity of the voltage transfer curve for large-signal swing.

$ECE\ 6412$  - Analog Integrated Circuits and Systems II

© P.E. Allen - 2002

Page 050-6

© P.E. Allen - 2002

Page 050-7

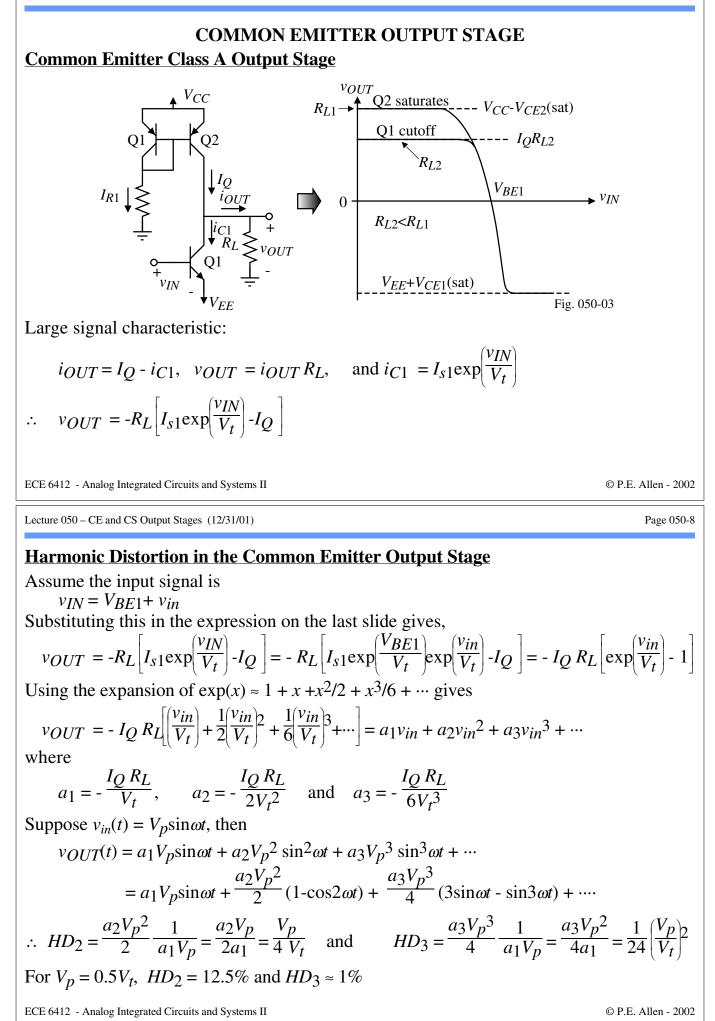

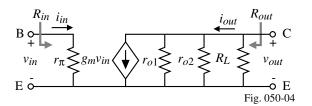

### **Small Signal Performance of the Common Emitter Output Stage**

Let  $r_{o1} || r_{o2} = r_o$ , then

$$R_{in} = r_{\pi 1} = \frac{\beta_o}{g_{m1}}, R_{out} = \frac{r_o R_L}{r_o + R_L} \approx R_L, \frac{v_{out}}{v_{in}} = \frac{-g_{m1} r_o \cdot R_L}{r_o + R_L} \approx -g_{m1} R_L \text{ and } \frac{i_{out}}{i_{in}} = \frac{\beta_o \cdot r_o}{r_o + R_L}$$

If  $V_{out}(\text{peak}) = 0.6\text{V}$ ,  $R_L = 1\text{k}\Omega$  and  $I_Q = 1.86\text{mA}$ , then

$$A_v \approx -g_{m1}R_L = -\frac{I_C}{V_t}R_L = -\frac{1.86}{26}1000 = -70.6\text{V/V} \implies Vp = \frac{0.6}{|A_v|} = \frac{0.6}{70.6} = 8.5\text{mV} \text{ (peak)}$$

$\therefore HD_2 = \frac{1}{4}\frac{8.5}{26} = 0.082 \text{ and } HD_3 = \frac{1}{24}\left(\frac{8.5}{26}\right)^2 = 0.0045$

Where does the distortion come from?

The ac gain at the negative peak output voltage is  $-\frac{1.86+0.6}{26}$  1000 = -94.6V/V

The ac gain at the positive peak output voltage is  $-\frac{1.86-0.6}{26}$  1000 = -48.5V/V Note the emitter follower is much more linear because of the inherent negative feedback.

ECE 6412 - Analog Integrated Circuits and Systems II

Lecture 050 - CE and CS Output Stages (12/31/01)

#### **SUMMARY**

**Requirements of Output Stages**

- The objectives are to provide output power in form of voltage and/or current.

- In addition, the output amplifier should be linear and be efficient.

- Low output resistance is required to provide power efficiently to a small load resistance.

- High source/sink currents are required to provide sufficient output voltage rate due to large load capacitances.

- Types of output stages considered:

Common emitter and common source

- Maximum efficiency is 25%

- Second-harmonic distortion can be significant

© P.E. Allen - 2002

Page 050-10