Lecture 130 – Compensation of Op Amps-II (1/30/02)

Page 130-1

# LECTURE 130 – COMPENSATION OF OP AMPS-II (READING: GLHM – 638-652, AH – 260-269)

### **INTRODUCTION**

The objective of this presentation is to continue the ideas of the last lecture on compensation of op amps.

### **Outline**

Compensation of Op Amps General principles Miller, Nulling Miller Self-compensation Feedforward

• Summary

ECE 6412 - Analog Integrated Circuits Design II

Lecture 130 – Compensation of Op Amps-II (1/30/02)

### Conditions for Stability of the Two-Stage Op Amp (Assuming $p_3 \ge GB$ )

• Unity-gainbandwith is given as:

$$GB = A_{v}(0) \cdot |p_{1}| = \left(\frac{gmIgmIIRIRIR}{gmIIRIRICc}\right) = \frac{gmI}{Cc} = \left(\frac{gm1gm2R1R2}{gm2R1R2Cc}\right) = \frac{gm1}{Cc}$$

• The requirement for 45° phase margin is:

$$\pm 180^{\circ} - \operatorname{Arg}[AF] = \pm 180^{\circ} - \tan^{-1}\left(\frac{\omega}{|p_1|}\right) - \tan^{-1}\left(\frac{\omega}{|p_2|}\right) - \tan^{-1}\left(\frac{\omega}{|p_2|}\right) = 45^{\circ}$$

Let  $\omega = GB$  and assume that  $z \ge 10GB$ , therefore we get,

$$\pm 180^{\circ} - \tan^{-1}\left(\frac{GB}{|p_{1}|}\right) - \tan^{-1}\left(\frac{GB}{|p_{2}|}\right) - \tan^{-1}\left(\frac{GB}{z}\right) = 45^{\circ}$$

$$135^{\circ} \approx \tan^{-1}(A_{\nu}(0)) + \tan^{-1}\left(\frac{GB}{|p_{2}|}\right) + \tan^{-1}(0.1) = 90^{\circ} + \tan^{-1}\left(\frac{GB}{|p_{2}|}\right) + 5.7^{\circ}$$

$$39.3^{\circ} \approx \tan^{-1}\left(\frac{GB}{|p_{2}|}\right) \Rightarrow \frac{GB}{|p_{2}|} = 0.818 \Rightarrow \boxed{|p_{2}| \ge 1.22GB}$$

• The requirement for 60° phase margin:

$|p_2| \ge 2.2GB$  if  $z \ge 10GB$

• If 60° phase margin is required, then the following relationships apply:

$$\frac{g_{m6}}{C_c} > \frac{10g_{m1}}{C_c} \implies g_{m6} > 10g_{m1} \qquad \text{and} \quad \frac{g_{m6}}{C_2} > \frac{2.2g_{m1}}{C_c} \implies C_c > 0.22C_2$$

ECE 6412 - Analog Integrated Circuits Design II

© P.E. Allen - 2002

Page 130-2

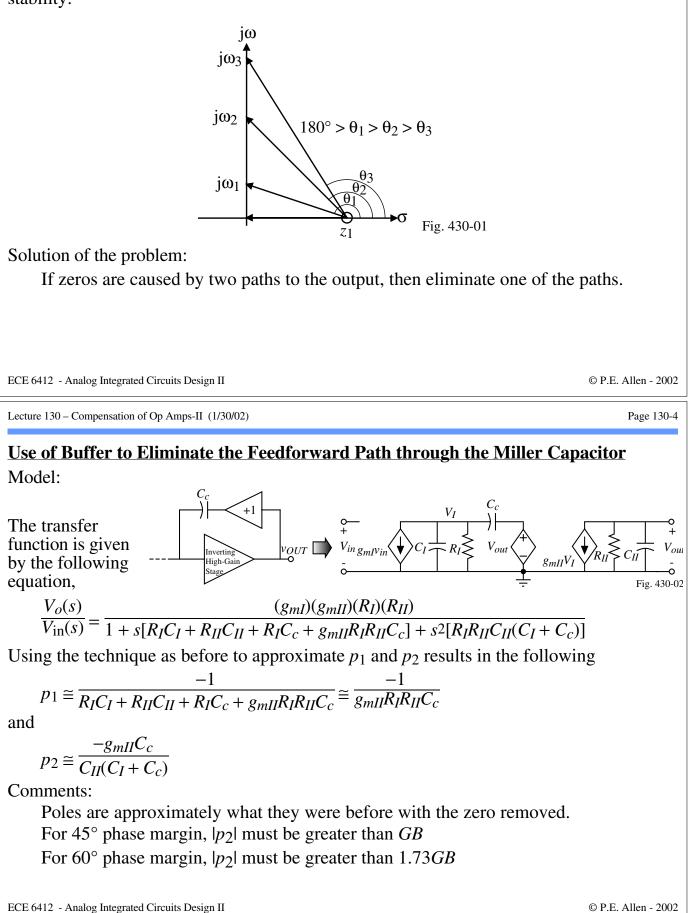

## **Controlling the Right-Half Plane Zero**

Why is the RHP zero a problem?

Because it boosts the magnitude but lags the phase - the worst possible combination for stability.

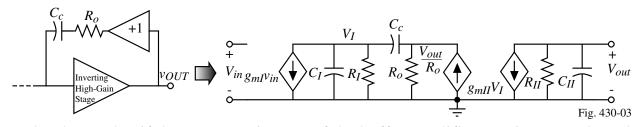

#### Use of Buffer with Finite Output Resistance to Eliminate the RHP Zero

Assume that the unity-gain buffer has an output resistance of  $R_o$ . Model:

It can be shown that if the output resistance of the buffer amplifier,  $R_o$ , is not neglected that another pole occurs at,

$$p_4 \cong \frac{-1}{R_o[C_I C_c / (C_I + C_c)]}$$

and a LHP zero at

$$z_2 \cong \frac{-1}{R_o C_c}$$

Closer examination shows that if a resistor, called a *nulling resistor*, is placed in series with  $C_c$  that the RHP zero can be eliminated or moved to the LHP.

ECE 6412 - Analog Integrated Circuits Design II

Lecture 130 – Compensation of Op Amps-II (1/30/02)

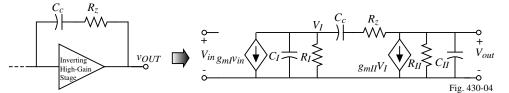

#### Use of Nulling Resistor to Eliminate the RHP Zero (or turn it into a LHP zero)<sup>†</sup>

Nodal equations:

$$g_{mI}V_{in} + \frac{V_I}{R_I} + sC_IV_I + \left(\frac{sC_c}{1 + sC_cR_z}\right)(V_I - V_{out}) = 0$$

$$g_{mII}V_I + \frac{V_o}{R_{II}} + sC_{II}V_{out} + \left(\frac{sC_c}{1 + sC_cR_z}\right)(V_{out} - V_I) = 0$$

Solution:

$$\frac{V_{out}(s)}{V_{in}(s)} = \frac{a\{1 - s[(C_c/g_{mII}) - R_zC_c]\}}{1 + bs + cs^2 + ds^3}$$

where

$$a = g_{mI}g_{mII}R_{I}R_{II}$$

$$b = (C_{II} + C_{c})R_{II} + (C_{I} + C_{c})R_{I} + g_{mII}R_{I}R_{II}C_{c} + R_{z}C_{c}$$

$$c = [R_{I}R_{II}(C_{I}C_{II} + C_{c}C_{I} + C_{c}C_{II}) + R_{z}C_{c}(R_{I}C_{I} + R_{II}C_{II})]$$

$$d = R_{I}R_{II}R_{z}C_{I}C_{II}C_{c}$$

© P.E. Allen - 2002

Page 130-6

<sup>&</sup>lt;sup>†</sup> W,J. Parrish, "An Ion Implanted CMOS Amplifier for High Performance Active Filters", Ph.D. Dissertation, 1976, Univ. of CA., Santa Barbara.

ECE 6412 - Analog Integrated Circuits Design II

© P.E. Allen - 2002

## Use of Nulling Resistor to Eliminate the RHP - Continued

If  $R_z$  is assumed to be less than  $R_I$  or  $R_{II}$  and the poles widely spaced, then the roots of the above transfer function can be approximated as

$$p_1 \cong \frac{-1}{(1 + g_{mII}R_{II})R_IC_c} \cong \frac{-1}{g_{mII}R_{II}R_IC_c}$$

$$p_2 \cong \frac{-g_{mII}C_c}{C_IC_{II} + C_cC_I + C_cC_{II}} \cong \frac{-g_{mII}}{C_{II}}$$

$$p_4 = \frac{-1}{R_zC_I}$$

and

$$z_1 = \frac{1}{C_c(1/g_{mII} - R_z)}$$

Note that the zero can be placed anywhere on the real axis.

ECE 6412 - Analog Integrated Circuits Design II

#### **Conceptual Illustration of the Nulling Resistor Approach**

$$V_{out} = \frac{-g_{m6}R_{II}\left(R_{z} + \frac{1}{sC_{c}}\right)}{R_{II} + R_{z} + \frac{1}{sC_{c}}}V' + \frac{R_{II}}{R_{II} + R_{z} + \frac{1}{sC_{c}}}V'' = \frac{-R_{II}\left[g_{m6}R_{z} + \frac{g_{m6}}{sC_{c}} - 1\right]}{R_{II} + R_{z} + \frac{1}{sC_{c}}}V$$

$V_{DD}$

M6

о V<sub>out</sub>

Fig. Fig. 430-05

when V = V' = V''.

Setting the numerator equal to zero and assuming  $g_{m6} = g_{mII}$  gives,

$$z_1 = \frac{1}{C_c(1/g_{mII} - R_z)}$$

ECE 6412 - Analog Integrated Circuits Design II

Page 130-8

© P.E. Allen - 2002

## A Design Procedure that Allows the RHP Zero to Cancel the Output Pole, p2

We desire that  $z_1 = p_2$  in terms of the previous notation. Therefore,

$$\frac{1}{C_c(1/g_{mII} - R_z)} = \frac{-g_{mII}}{C_{II}} \xrightarrow{P_4} \frac{p_2}{P_2} \xrightarrow{P_1} \frac{j\omega}{z_1} \xrightarrow{C_1} Fig. 430-06$$

The value of  $R_z$  can be found as

$$R_z = \left(\frac{C_c + C_{II}}{C_c}\right) (1/g_{mII})$$

With  $p_2$  canceled, the remaining roots are  $p_1$  and  $p_4$  (the pole due to  $R_z$ ). For unity-gain stability, all that is required is that

$$|p_4| > A_{\nu}(0)|p_1| = \frac{A_{\nu}(0)}{g_{mII}R_{II}R_IC_c} = \frac{g_{mI}}{C_c}$$

and

$$(1/R_zC_I) > (g_{mI}/C_c) = GB$$

Substituting  $R_z$  into the above inequality and assuming  $C_{II} >> C_c$  results in

$$C_c > \sqrt{\frac{g_{mI}}{g_{mII}}} C_I C_{II}$$

This procedure gives excellent stability for a fixed value of  $C_{II} (\approx C_L)$ .

Unfortunately, as  $C_L$  changes,  $p_2$  changes and the zero must be readjusted to cancel  $p_2$ .

ECE 6412 - Analog Integrated Circuits Design II

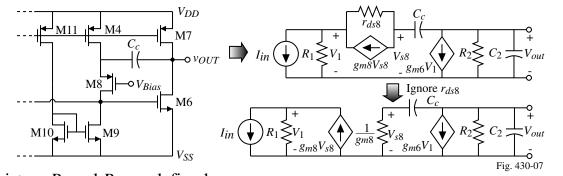

## **Increasing the Magnitude of the Output Pole**<sup>†</sup>

The magnitude of the output pole,  $p_2$ , can be increased by introducing gain in the Miller capacitor feedback path. For example,

The resistors  $R_1$  and  $R_2$  are defined as

$$R_1 = \frac{1}{g_{ds2} + g_{ds4} + g_{ds9}}$$

and  $R_2 = \frac{1}{g_{ds6} + g_{ds7}}$

where transistors M2 and M4 are the output transistors of the first stage. Nodal equations:

$$I_{in} = G_1 V_1 - g_{m8} V_{s8} = G_1 V_1 - \left(\frac{g_{m8} s C_c}{g_{m8} + s C_c}\right) V_{out} \quad \text{and} \quad 0 = g_{m6} V_1 + \left[G_2 + s C_2 + \frac{g_{m8} s C_c}{g_{m8} + s C_c}\right] V_{out}$$

ECE 6412 - Analog Integrated Circuits Design II

© P.E. Allen - 2002

© P.E. Allen - 2002

Page 130-10

B.K. Ahuja, "An Improved Frequency Compensation Technique for CMOS Operational Amplifiers," IEEE J. of Solid-State Circuits, Vol. SC-18, No. 6 (Dec. 1983) pp. 629-633.

#### **Increasing the Magnitude of the Output Pole - Continued**

Solving for the transfer function  $V_{out}/I_{in}$  gives,

$$\frac{V_{out}}{I_{in}} = \left(\frac{-g_{m6}}{G_1 G_2}\right) \left[\frac{\left(1 + \frac{sC_c}{g_{m8}}\right)}{1 + s\left[\frac{C_c}{g_{m8}} + \frac{C_2}{G_2} + \frac{C_c}{G_2} + \frac{g_{m6}C_c}{G_1 G_2}\right] + s^2\left(\frac{C_cC_2}{g_{m8}G_2}\right)}\right]$$

Using the approximate method of solving for the roots of the denominator gives

$$p_1 = \frac{\frac{-1}{C_c}}{\frac{C_c}{g_{m8}} + \frac{C_c}{G_2} + \frac{C_2}{G_2} + \frac{g_{m6}C_c}{G_1G_2}} \approx \frac{\frac{-6}{g_{m6}r_{ds}^2C_c}}{\frac{g_{m6}r_{ds}^2C_c}{G_1G_2}}$$

and

$$p_{2} \approx \frac{-\frac{g_{m6}r_{ds}^{2}C_{c}}{6}}{\frac{C_{c}C_{2}}{g_{m8}G_{2}}} = \frac{g_{m8}r_{ds}^{2}G_{2}}{6} \left(\frac{g_{m6}}{C_{2}}\right) = \left(\frac{g_{m8}r_{ds}}{3}\right)|p_{2}'|$$

where all the various channel resistance have been assumed to equal  $r_{ds}$  and  $p_2$ ' is the output pole for normal Miller compensation. Result:

Dominant pole is approximately the same and the output pole is increased by  $\approx g_m r_{ds}$ .

ECE 6412 - Analog Integrated Circuits Design II

## **Concept Behind the Increasing of the Magnitude of the Output Pole**

$$V_{DD} = r_{ds} r_{ds$$

Page 130-12

ECE 6412 - Analog Integrated Circuits Design II

### **SUMMARY**

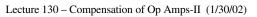

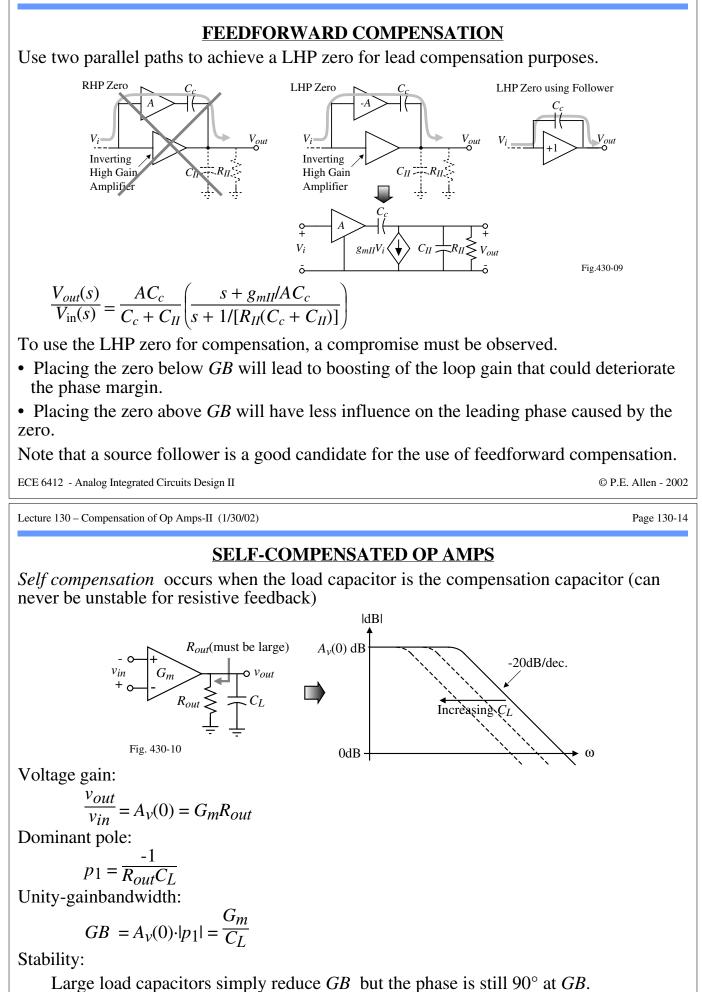

# Compensation

- Designed so that the op amp with unity gain feedback (buffer) is stable

- Types

- Miller

- Miller with nulling resistors

- Self Compensating

- Feedforward

ECE 6412 - Analog Integrated Circuits Design II