NAME:

## **GEORGIA INSTITUTE OF TECHNOLOGY** School of Electrical and Computer Engineering

ECE 4430 Fall 2002 First Exam September 27, 2002 Closed Book and Notes

General Instructions:

- 1. Write on one side of the paper. (1 Pt.)

- 2. Put answers to all questions in the spaces provided on the test. (1 Pt.)

- 3. Show all work for full credit on questions requiring calculations. No credit will be given for answers alone, without supporting work.

- 4. Problems and questions are weighted as indicated. The maximum score is 100 points.

- 5. If you need more paper (provided in class), remove the staple from the exam and, when finished, arrange the test in order. Place the extra pages with supporting work in the test behind the page where the problem appears and indicate accordingly. Staple the entire test together so that there are no loose pages. (1 Pt.)

TEST SCORE: \_\_\_\_\_ / 100

I certify that I have neither given nor received any assistance while taking this test from anyone.

(Signature) (1 Pt.)

□ Place a check mark in the box if you observed any suspicious actions while taking this test.

Formula Sheet: Equations/Constants that you may, or may not, need are listed below:

$$\begin{split} &K' = 50 \; \mu A/V^2 \; (\text{unless otherwise stated in the problem}) \\ &K_n = K'W/L \\ &\lambda = 0.01 \; V^{-1} \; (\text{unless otherwise stated in the problem}) \\ &V_{TO} = 0.7 \; V \; (\text{unless otherwise stated in the problem}) \\ &\gamma = 0.5 \; V^{1/2} \; (\text{unless otherwise stated in the problem}) \\ &2\phi_F = 0.6 \; V \; (\text{unless otherwise stated in the problem}) \\ &I_{D-Triode} = (K_n/2) \; [2(V_{GS} - V_{TN})V_{DS} - V_{DS}^2] \\ &I_{D-Sat} = (K_n/2) \; (V_{GS} - V_{TN})^2 \; (1 + \lambda V_{DS}) \\ &V_{TN} = V_{TO} + \gamma \; [\text{sqrt}(2\phi_F - V_{BS}) - \text{sqrt}(2\phi_F)] \\ &r_{o-MOS} \approx 1 \; / \; (\lambda I_{DS}) \\ &g_{m-MOS} = \text{sqrt}[2I_{DS}K_n] \\ &V_{ds-sat} = \text{sqrt}(2I_{DS}/K_n) \\ &g_{mb-MOS} = \eta g_{m-MOS} \\ &\eta = \gamma \div 2 \; \text{sqrt}(2\phi_F - V_{BS}) \end{split}$$

$V_t = kT/q \approx 26 \text{ mV and } I_S = 1E-15 \text{ A (unless otherwise stated in the problem)}$   $I_{Diode} = I_S [exp(V_D/V_t) - 1]$  $C_j = \frac{C_{j0}}{\left(1 - \frac{v_D}{\psi_0}\right)^m} \rightarrow 0.33 \le m \le 0.5$

$$\begin{split} V_A &= 100 \ V \ (\text{unless otherwise stated in the problem}) \\ \beta_F &= 50 \ (\text{unless otherwise stated in the problem}) \\ I_{CE} &= I_S \ [\exp(V_{BE}/V_t) - 1] \ [1 + V_{CE}/V_A] \\ r_{o\text{-NPN}} &= V_A \ / \ I_{CE} \\ g_{\text{m-NPN}} &= I_{CE}/V_t \end{split}$$

# **Device Physics - Part A (38 Points)**

| 1. In a p+n junction diode, if the reverse-biased voltage decreases, the depletion width <u>decreases /</u>                 |         |

|-----------------------------------------------------------------------------------------------------------------------------|---------|

| <u>increases / remains constant</u> .                                                                                       | (2 pts) |

| 2. In a pn junction diode, a high breakdown voltage is caused by                                                            |         |

| The predominant breakdown mechanism in very highly doped diodes is                                                          |         |

| breakdown.                                                                                                                  | (4 pts) |

| 3. <u><i>True or False</i></u> : In a p++n junction diode ( $N_A \gg N_D$ ), the depletion capacitance is mostly determined |         |

| by N <sub>A</sub> .                                                                                                         | (2 pts) |

| 4. As the forward-biased voltage of a $p+n$ junction diode increases, the depletion capacitance <u>decreases</u>            |         |

| <u>/increases/remains constant</u> .                                                                                        | (2 pts) |

| 5. What physical phenomenon do Early voltage effects describe (qualitatively, what happens to the                           |         |

| device)?                                                                                                                    | (4 pts) |

|                                                                                                                             |         |

|                                                                                                                             |         |

|                                                                                                                             |         |

| 6. The current gain $\beta$ of an NPN BJT <u>decreases / increases / remains constant</u> with rising temperatures.         |         |

|                                                                                                                             | (2 pts) |

| 7. <u><i>True or False</i></u> : The current gain $\beta$ of an NPN BJT is dependent on both emitter injection efficiency   |         |

| and base-transport factor.                                                                                                  | (2 pts) |

8. Breakdown voltage BV<sub>CEO</sub> is *less than / greater than / equal to* BV<sub>CBO</sub>. (2 pts)

9. If a MOS transistor is in the saturation region and its drain current exhibits a linear dependence with respect to gate-source voltage, what physical phenomenon is more than likely occurring?

How can a designer ensure a square-law . behavior? (6 pts)

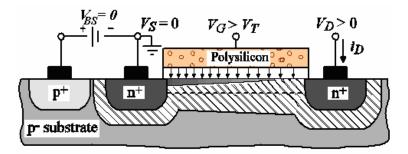

10. In what region of operation is the device shown below operating? \_\_\_\_\_(2 pts)

11. On the figure above, the effective threshold voltage <u>decreases / increases / remains constant</u> when the bulk-source voltage  $V_{BS}$  is increased from zero to 400 mV. (2 pts) 12. If a MOSFET's channel is only weakly inverted, its current is mainly due to <u>drift / diffusion /</u>

## <u>neither</u>.

. (2 pts)

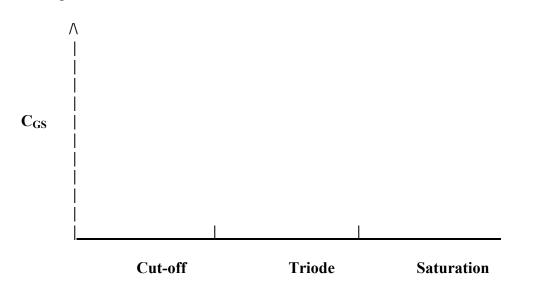

13. In the space provided, roughly sketch the value of capacitor  $c_{gs}$  as an NMOS device transitions from cut-off, through triode, on to saturation. (6 pts)

#### <u>Circuits – Part B (42 Points)</u>

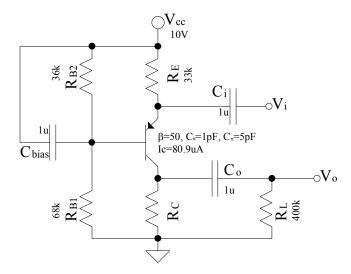

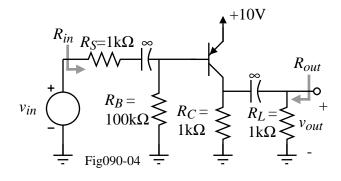

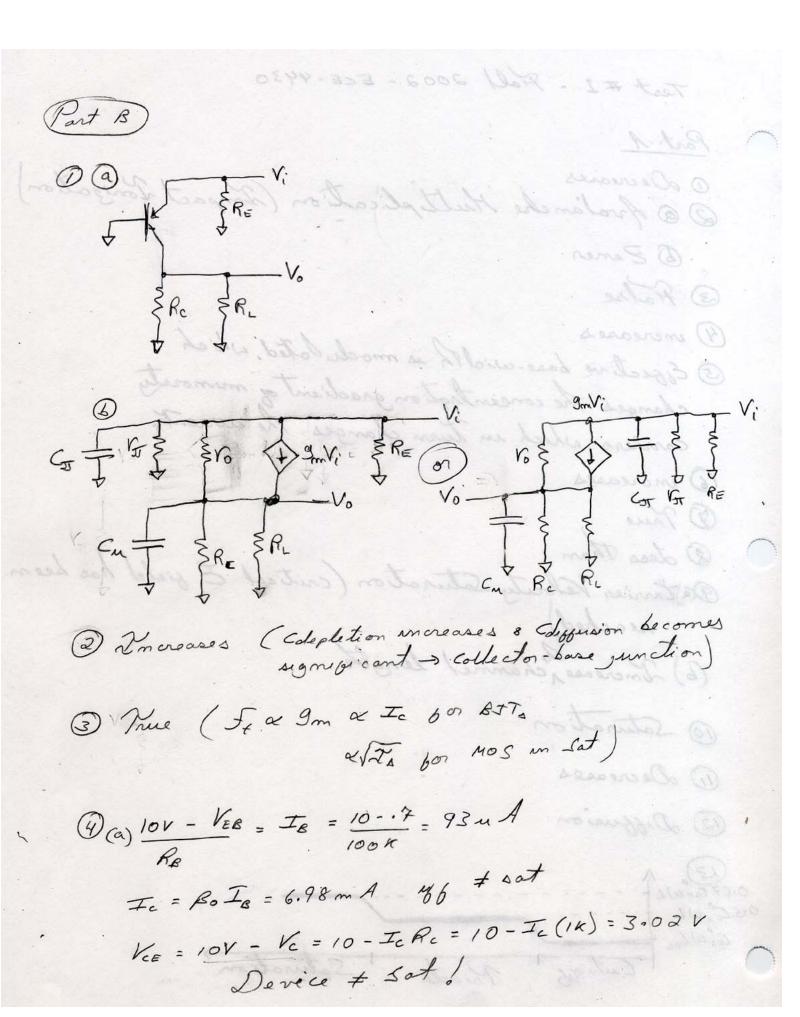

(a) For the circuit shown below, draw the ac equivalent circuit -do <u>NOT</u> replace the transistor with its small-signal equivalent model-. (5 pts)

(b) Now replace the PNP with its small-signal model –use only variables,  $g_m$ ,  $r_o$ ,  $r_\pi$ ,  $C_\mu$ ,  $C_\pi$ , etc., where appropriate and applicable –do <u>*NOT*</u> use or calculate their respective absolute values–)–. (5 pts)

2.) As an NPN BJT starts to saturate, capacitor  $C_{\mu}$  <u>decreases / increases / remains the same</u>. (2 pts)

3.) <u>*True or False*</u>: Neglecting high-level injection effects, transition frequency  $f_t$  increases with increasing currents for both MOSFETs and BJTs. (2 pts)

4.) (a) Derive the biasing point of the PNP transistor ( $I_C$  and  $V_{CE}$ ) in the figure below if  $\beta_F$  is 75,  $V_A$  is 50 V, and the base-emitter voltage is roughly 0.7 V. (8 pts)

(b) Now draw the small-signal equivalent circuit (use variables only,  $g_m$ ,  $r_o$ ,  $r_\pi$ ,  $R_S$ ,  $R_B$ ,  $R_C$ , and  $R_L$  –do <u>NOT</u> use or calculate their respective absolute values–). (10 pts)

(c) Now derive the voltage gain from  $v_{in}$  to  $v_{out}$  (A =  $v_{out} / v_{in}$ , use variables only,  $g_m$ ,  $r_o$ ,  $r_\pi$ ,  $R_S$ ,  $R_B$ ,  $R_C$ , and  $R_L$  –do <u>NOT</u> use or calculate their respective absolute values–). (10 pts)

### **Device Fabrication – Part C (16 Points)**

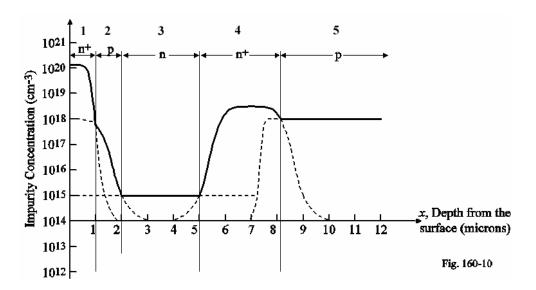

1.) Given the doping profile shown below, which region(s) has(ve) more than likely been ion

implanted?

$$1/2/3/4/5$$

(2 pts)

2.) What is the purpose of region 4 –assuming its doping profile was shaped intentionally–? (4 pts)

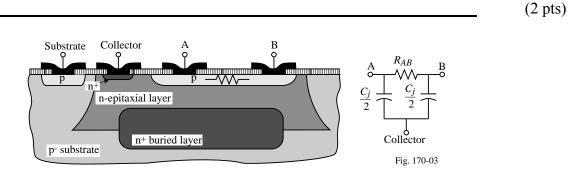

3.) Given the device below, if the p-base region was used as a large-valued resistor, as shown, where should the collector terminal be connected? <u>Positive supply voltage / Negative supply voltage</u> (2 pts) Why?

4.) If the collector-base junction was used as a junction capacitor, would adding the n+ buried layer

## *increase / decrease / not affect* its Q performance.

(2 pts)

(4 pts)

Why?

Test #1 - Field 2002 - ECE-4430

Part A @ @ Avalanche Hultiplication (Impact Tonization) 1 Decreases 1 Zener 3 Halse (4) increases 3 Espective base-width is modulated, which changes the concentration gradient of memority carriers, which in Turn changes the current. 6 increases D True @ Less Than Dastarrier Velocity Saturation (critical & field has been reached) (6) Increase channel length @ Saturation (1) Decreases 2 Diffusion 0.67 Gx WL OSG",WL Gr WLOL Saturation Cut-gh

Part B) Vi my Vi Vi my Vi RB Vi RB Vi  $(c) \frac{V_0}{V_i} = \frac{V_0}{V_b} \frac{V_b}{V_i} = \left[ -\frac{9}{m} \left( \frac{V_0}{V_c} \| R_c \| R_c \right) \right] \left[ \frac{R_a \| V_{ST}}{R_a \| T_{ST} + R_s} \right]$ Part C) O 4 600 sure and passibly 1 Decrease collector resistance of an NTPN. Degrade borward Bog substrate PNP 3 (as positive supply (b) Reverse bias the junction (Is alate device) Pinch resistance (Amoreare its value) D'Amorease (de creases series R - + ESR)