## **PARLAK: Parametrized Lock Cache Generator**

Bilge E. S. Akgul and Vincent J. Mooney III School of Electrical and Computer Engineering Georgia Institute of Technology, USA

#### Introduction

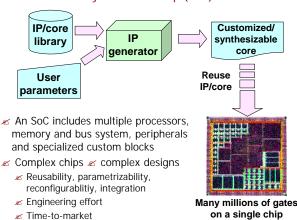

#### Intellectual Property (IP) or core based design for System-on-a-Chip (SoC)

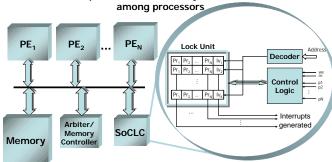

Custom hardware: SoC Lock Cache (SoCLC)

SoCLC provides lock-based synchronization

- ✓ SoCLC is an IP core that provides effective lock-based synchronization for a shared-memory multiprocessor SoC

- ∠ Lock variables are accessed from the SoCLC

- ✓ Interrupts are generated to notify processors when a lock is released.

- ✓ Achieved speedups of 27% to 55% in practical examples

skeleton files

Generate code/module

using the library and

parameters

Output synthesizable

codes for SoCLC and

top configuration

✓ More information at <a href="http://codesign.ece.gatech.edu/publications/">http://codesign.ece.gatech.edu/publications/</a>

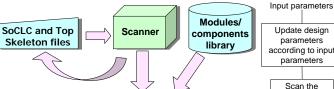

# **Methodology**PARLAK: Parametrized Lock Cache Generator

∠ PARLAK is an IP-generator tool for SoCLC

✓ Solution: IP-generator tools

Automated generation of synthesizable

IP blocks and system components

- Generates customized, user specified versions of SoCLC

- Useful for after/prior to chip fabrication

- Building blocks:

- ∠ Input parameters

- Number of short critical section locks, number of long critical section locks

- Number and types of processors

- Interrupt generation (FIFO or priority based)

- ✓ Skeleton files (in Verilog HDL)

- Signal, process and module descriptions (independent from the input parameters)

- ∠ Library of modules/components

Input parameters

Generator

Top configuration

Sample skeleton input file and generated output file

Module LockCache (cikrstre.we. \_ D.A.IRO.pr):

/// ABEL #2 – Interrupt lines updated with priority

/// LABEL #3 – Control logic instantiations

/// Module LockCache (cikrstre.we. \_ D.A.IRO.pr):

/// LABEL #3 – Control logic instantiations

/// Module LockCache (cikrstre.we. \_ D.A.IRO.pr):

/// LABEL #3 – PARAMETER declarations

parameter NIML\_DECKS = 64:

parameter SMALL\_DCKS = 64:

parameter SMALL\_DCKS = 32:

parameter MDR.W = 5:

/// LABEL #2 – Interrupt lines updated with priority

I// LABEL #3 – Control logic instantiations

control ctrl (cikcl), s.19(19.), infinctrl),

outif(rq.wl0]). we(we):

outif(rq.wl0]). we(we):

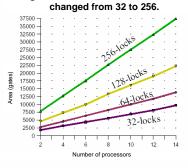

### Synthesis Results of SoCLC Configurations Generated Using PARLAK

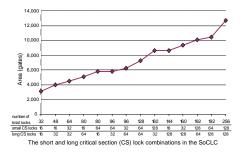

- Full range of customized SoCLCs that are generated by PARLAK have been directly synthesized using Design Compiler from Synopsys

- An SoCLC for two processors with 32 lock variables occupies 1,790 gates and an SoCLC for 14 processors with 256 lock variables occupies 37,380 gates

- PARLAK output SoCLC and top configurations are also simulated to test correctness in the Seamless CVE platform from Mentor Graphics

- Four MPC750 processors, shared memory, SoCLC, decoder and arbiter

Synthesis results of SoCLC for increasing number of locks. Number of processors = 4.

Synthesis results of SoCLC for increasing number of processors that the SoCLC is configured for. Number of lock variables is