# A Configurable Hardware Scheduler (CHS) for Real-Time Systems

Pramote Kucharoen, Mohamed A. Shalan and Vincent J. Mooney III

Center for Research on Embedded Systems and Technology School of Electrical and Computer Engineering Georgia Institute of Technology Atlanta, Georgia, USA

23 June 2003

# Outline

- Introduction

- Related work

- CHS architecture

- CHS commands

- CHS interface

- Software support

- Automatic customization of CHS

- Experiments and results

- Conclusion

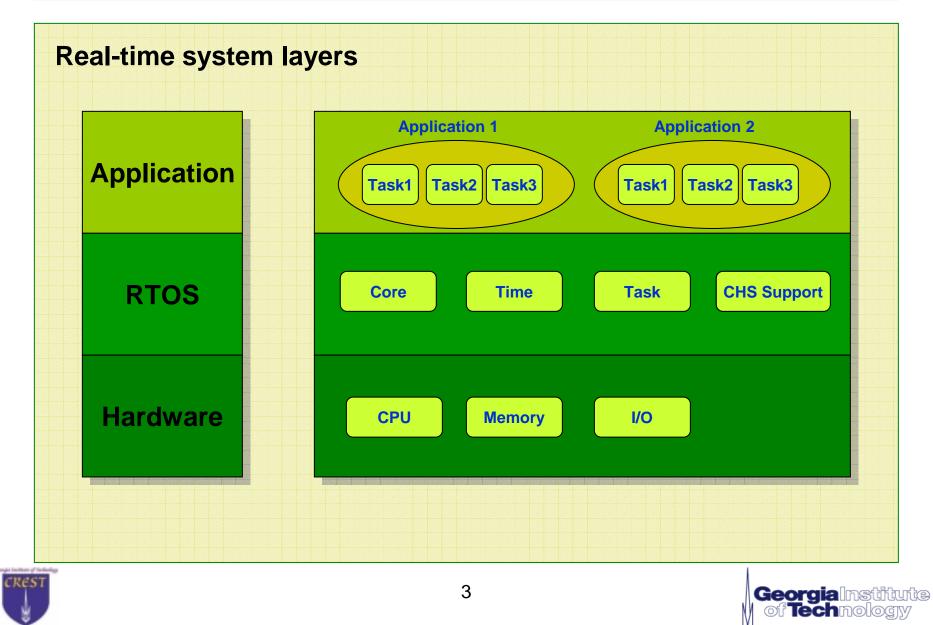

#### Introduction

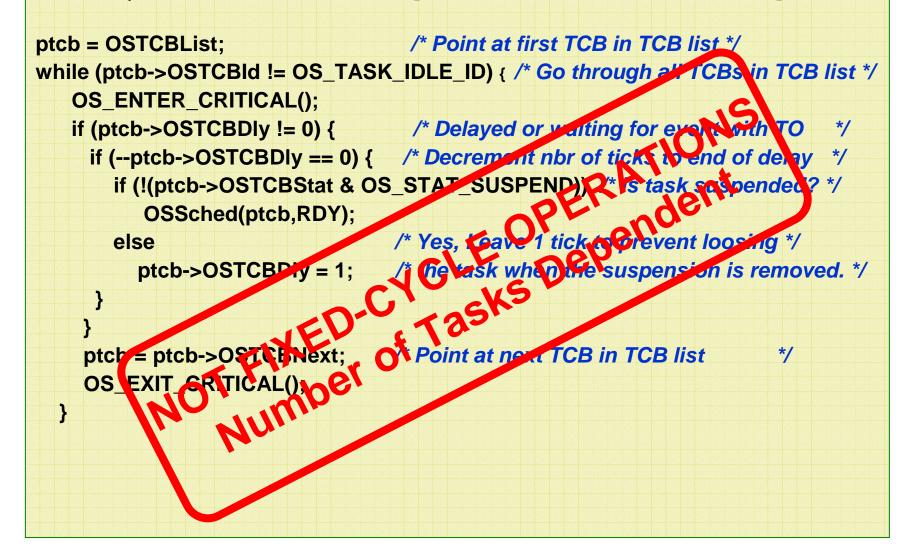

#### μC/OS II Background Processing

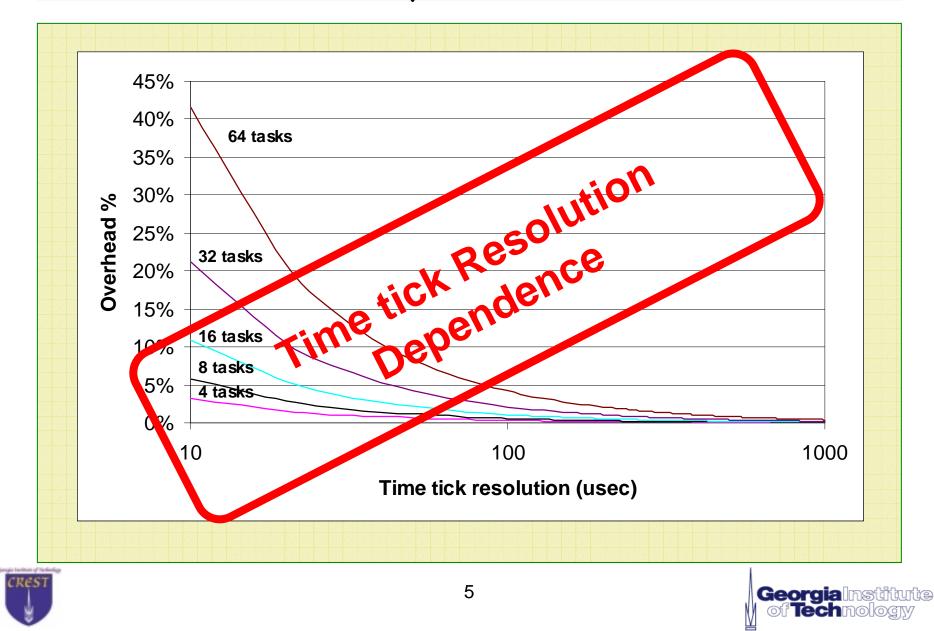

# **Overhead in µC/OS II Scheduler**

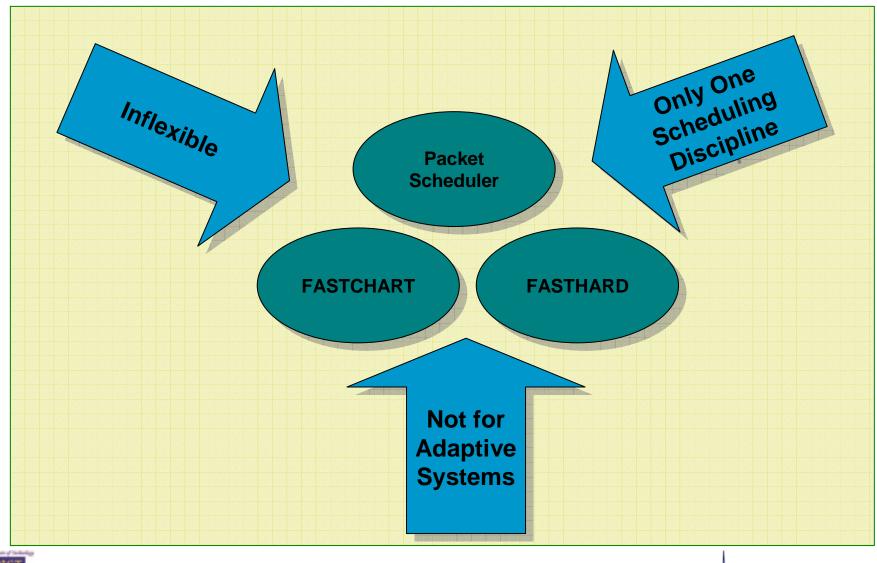

#### **Related Work**

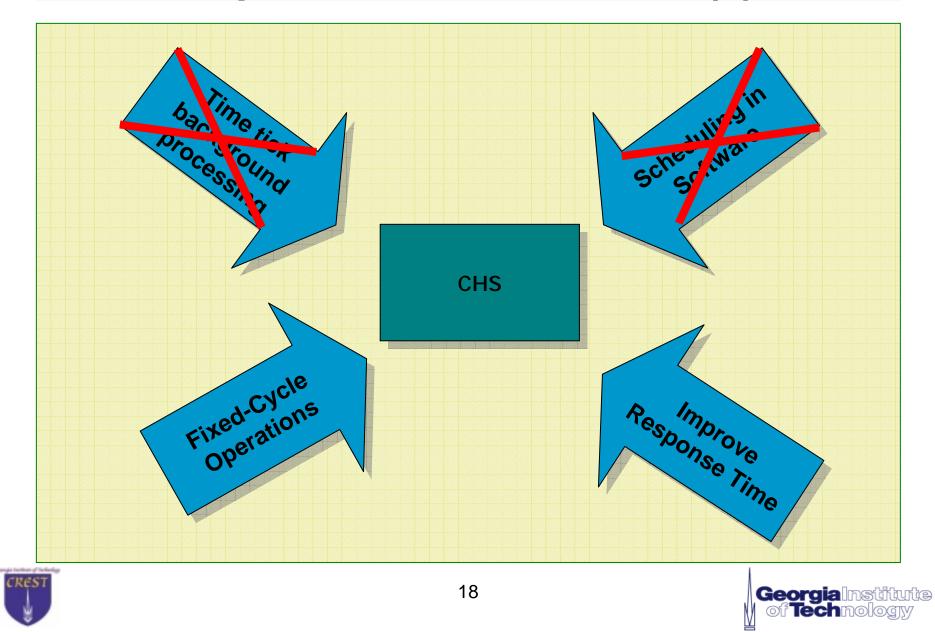

#### Why do we need the CHS?

- To reduce the scheduling overhead from the realtime operating system; hence, improve the system response time

- To support a wide range of applications by supporting multiple scheduling disciplines that can be changed during system execution time.

- Priority

- Earliest Dead Line First (EDF)

- Rate Monotonic (RM)

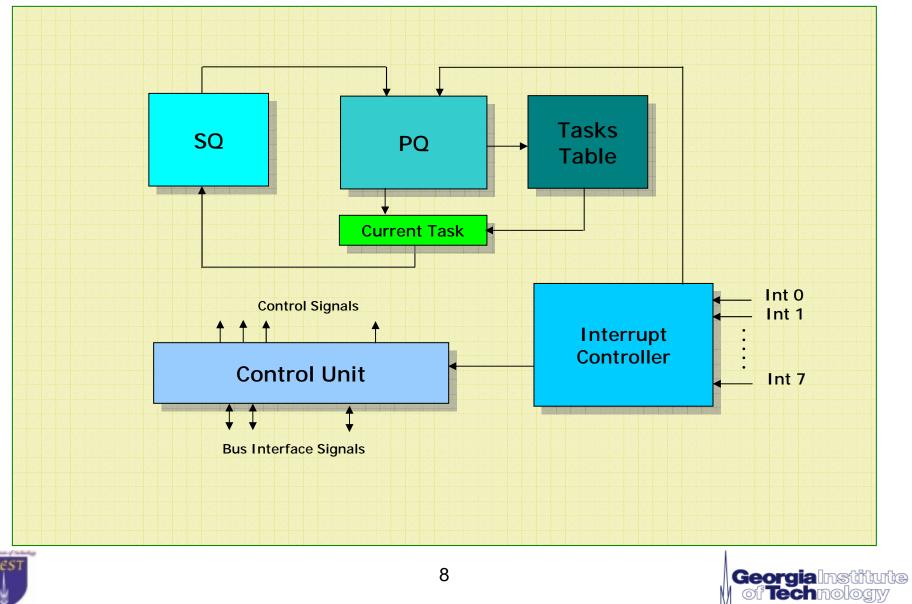

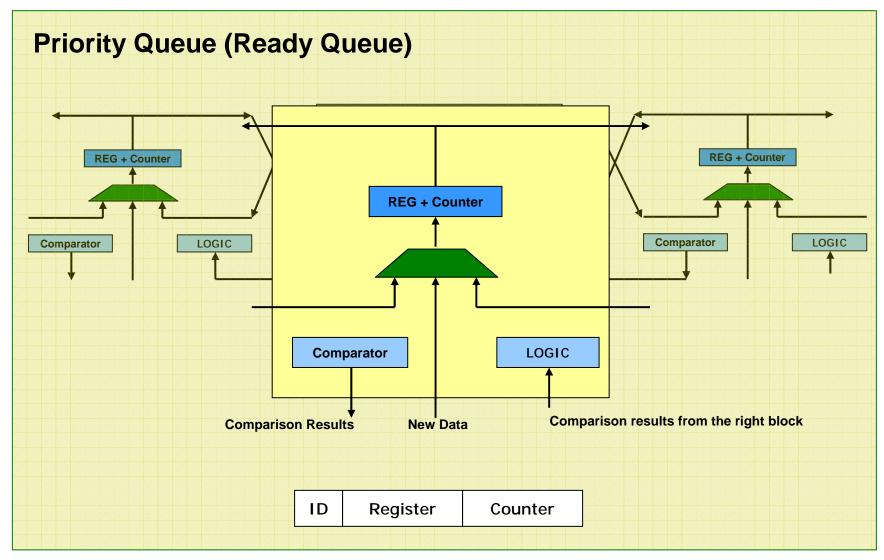

# **CHS Architecture (1)**

# **CHS Architecture (2)**

# **CHS Architecture (3)**

#### **Sleep Queue**

- Used to store the Sleeping Tasks (YIELD/SLEEP).

- The Tasks are sorted according to their remaining sleep time.

- Once The Sleep Time expires it is moved to the PQ.

# **CHS Architecture (4)**

## **CHS Commands**

|                   | Command     | # of Cycles |

|-------------------|-------------|-------------|

|                   | STOP        | 1           |

| Scheduler Related | RUN         | 1           |

|                   | CONFIGURE   | 1           |

|                   | CREATE Task | 1           |

|                   | MODIFY Task | 2           |

|                   | SLEEP       | 2           |

| Tool Deleted      | SSLEEP      | 1           |

| Task Related      | YIELD       | 1           |

|                   | SUSPEND     | 1           |

|                   | RESUME      | 1           |

|                   | DELETE      | 1           |

#### **CHS** Interface

The CHS Hardware is designed to be able to interface easily to any microprocessor core:

- As a memory mapped I/O Port,

- As a co-processor, or

- As instruction-set accelerator

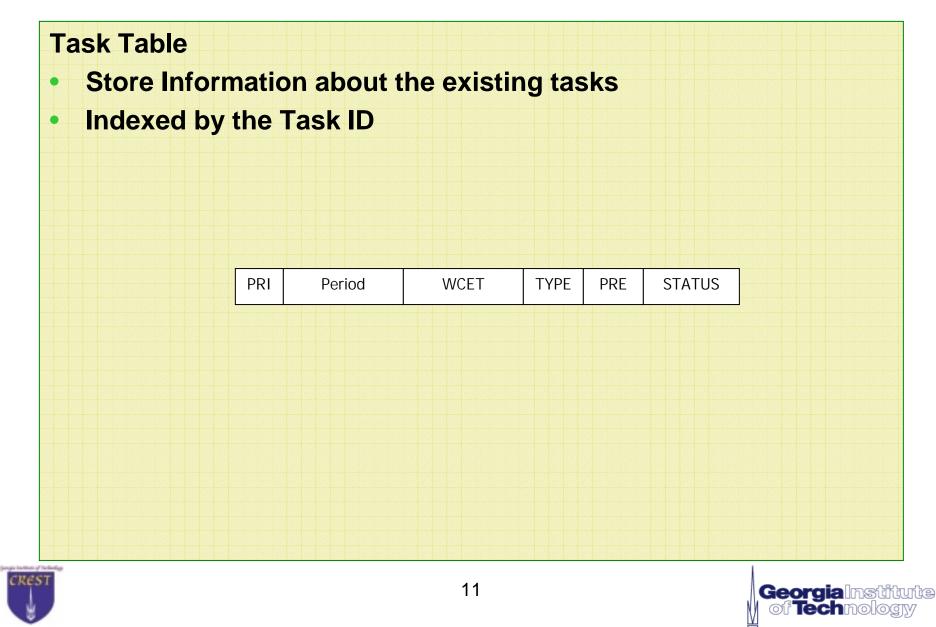

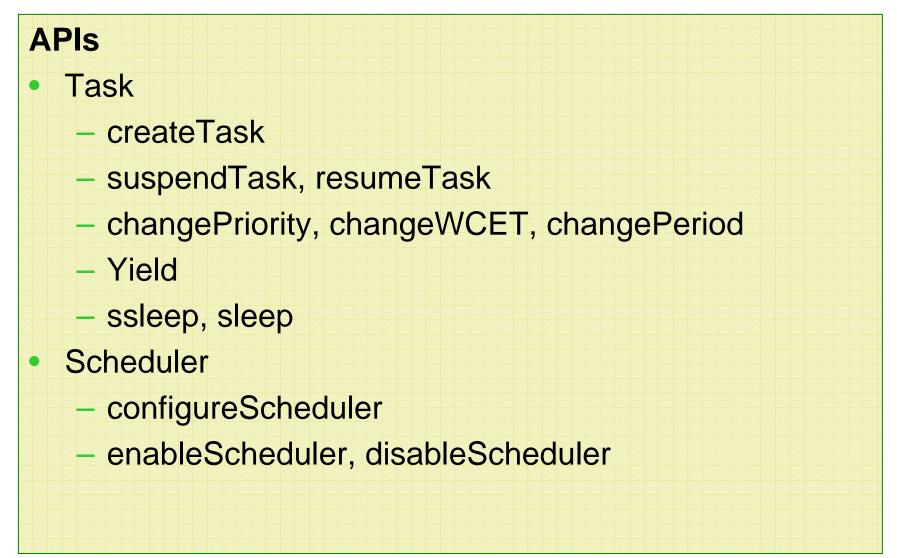

# Software Support

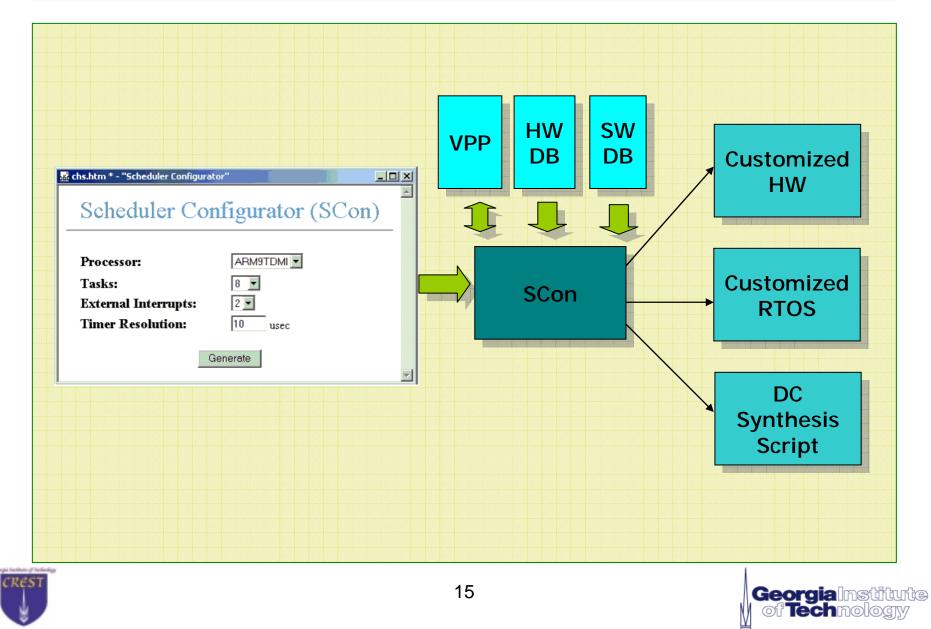

#### **Automatic Customization of CHS**

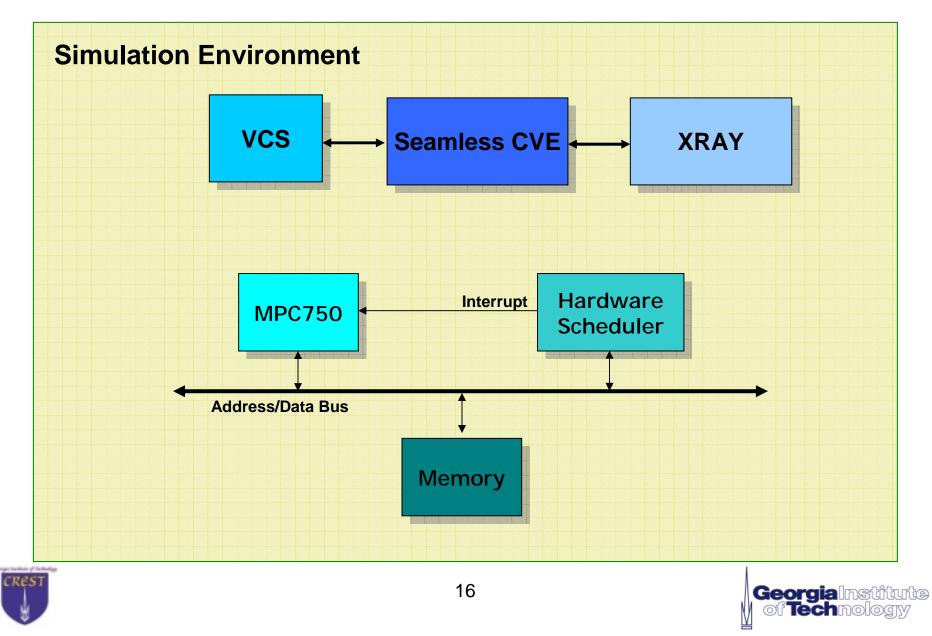

#### **Experiments and Results (1)**

# **Experiments and Results (2)**

|                      | Micro C/OS II                                 | Hardware Scheduler                  |  |

|----------------------|-----------------------------------------------|-------------------------------------|--|

| Scheduler*           | 69                                            | 0                                   |  |

| Time-tick processing | 47+47*(number of tasks)                       | 0                                   |  |

|                      |                                               |                                     |  |

| Numbe<br>API         | r of PowerPC instruction<br># of PPC Assembly | n of the APIs<br>WCET (# of cycles) |  |

|                      |                                               |                                     |  |

|                      | # of PPC Assembly                             |                                     |  |

#### **Experiments and Results (3)**

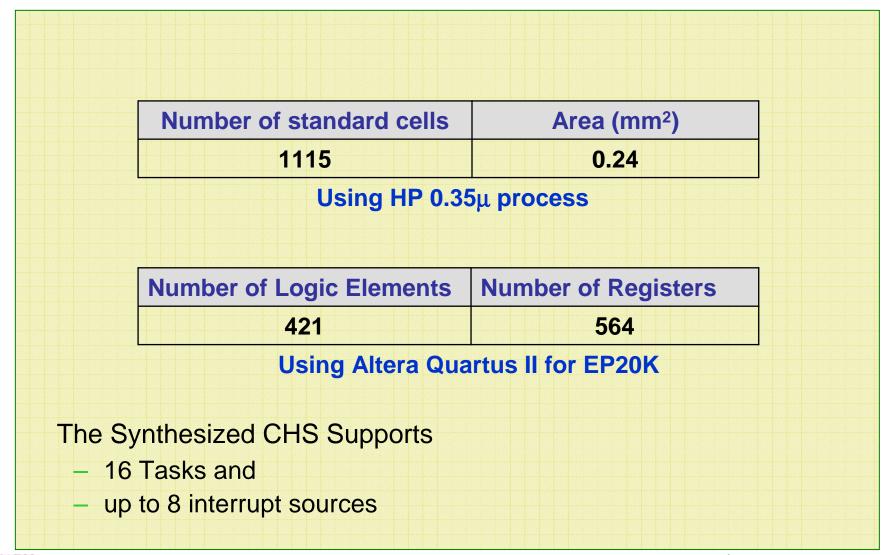

# **CHS Synthesis Results**

#### Conclusion

- We implemented a configurable hardware scheduler that supports 3 scheduling algorithms

- We developed software interface for the configurable hardware scheduler and a tool to generate a customized synthesizable CHS

- The configurable hardware scheduler eliminated the time spent by the processor for background time tick processing and scheduling

## **Questions?**